これからの組み込み機器のメモリ構成は「SRAM/FRAM+NORフラッシュ」:SnDアーキテクチャはもう限界だ

産業機器をはじめとした組み込み機器のメモリ構成が変わりつつある。これまで、組み込み機器のメモリは「DRAM+NANDフラッシュ」という構成が一般的だったが、今後組み込み向けの低容量、高信頼DRAM/NANDフラッシュの調達難が予想され、代替メモリへの切り替えが必要になっている。そこで、新たなメモリ構成として有力視されているのが、さらなる進化が見込まれるSRAM/FRAM、そしてNORフラッシュだ。

コンピュータ領域でのメモリ構成見直しが組み込み領域にも影響

産業機器をはじめとした組み込み機器も、メモリ構成を見直すべき時期が到来している――。

サーバやPCといったコンピュータ領域では、メモリ/ストレージ階層の見直しの議論が活発だ。抵抗変化メモリ、磁気メモリ、相変化メモリなどのいわゆる次世代半導体メモリの登場で、これまでのDRAMによる主記憶装置と、NAND型フラッシュメモリ(以下、NANDフラッシュ)やHDDで構成され外部記憶装置の中間に位置するストレージ・クラス・メモリ(SCM)が提唱され、数年後には「DRAM〜SCM〜NANDフラッシュ〜HDD」といった階層のメモリ構成が一般化する見込みだ。

こうしたコンピュータ領域でのメモリ階層の見直しは、組み込み領域にとっても決して無関係の動きではない。

現状、組み込み領域で一般的なメモリ構成は、DRAMとNANDフラッシュを使った構成であり、これまでのコンピュータと同じメモリ構成だ。では、組み込み領域でもSCMの導入が進むのかといえば、そうではない。組み込み領域では、高価なSCMを導入するほど、性能を求めてはいないからだ。

なおざりの組み込み向けDRAM、NANDフラッシュは供給がタイトに……

であれば、やはり、コンピュータ領域でのメモリ階層の見直しは、組み込み領域には無縁のもの……と思うかもしれないが、ここで注意しなければならないのが、組み込み領域で使うDRAM、NANDフラッシュは、コンピュータ領域で使われるDRAM、NANDフラッシュとほぼ同じものを使っているという事実だ。コンピュータ領域で、新たなメモリ階層であるSCMが出現すれば、DRAM、NANDフラッシュの役割、性質はこれまでと変わることになる。DRAM、NANDフラッシュの役割、性質が変わってしまえば、おのずと組み込み領域でもその変化に追従しなくてはならない。そのため、コンピュータ領域のメモリ階層見直しは組み込み領域にとっても無関係ではなく、既にこれまでのDRAMとNANDフラッシュを使ったメモリ構成を見直す必要に迫られそうな兆候も現れ始めている。

まず、DRAM市場を見ると、技術的な限界から容量拡大のペースが大きく鈍っている。SCMの利用が提唱されるようになったのも、このDRAM容量の頭打ちが主因だ。従って、DRAMメーカーのほとんどは、SCMを担う次世代半導体メモリに活路を見いだしており、DRAMへの投資は縮小傾向にある。しかし、次世代半導体メモリがすぐにDRAMを置き換えるまでには至らず、今後もDRAM需要はサーバの出荷増などに合せて増える見通しだ。そうなれば、増産投資が行われないDRAMは、供給不足に陥る可能性が高く、安定調達が望みにくくなるのだ。

一方のNANDフラッシュは、これまで以上に大容量化が顕著に求められるようになる。NANDフラッシュの大容量化は、これまで微細化と多値化で実現され、昨今は記憶セルを縦方向に積む多層化によって実現されつつある。ただ、微細化技術に関しては、DRAM同様その進化速度は鈍り、現状の大容量化は、多層化、すなわち3D NAND化に頼る比重が大きくなっている。そのため、NANDフラッシュメーカーは、これまでのプレーナー型NAND(2D NAND)から3D NANDへの移行を急ピッチで進めている。

多層化技術により、容量当たりのコストが大きく削減されれば、コンピュータ領域よりも比較的、小さな容量を求める組み込み領域でも3D NANDが採用できるが、残念ながら3D NANDは、2D NANDよりも割高になる公算が大きい。構造上、多層化を進めるほど、容量当たりのコスト削減率が低下するというジレンマも抱えるためであり、組み込み領域では、使い切れないほど大容量で、かつ、容量当たりの単価が割高な3D NANDをわざわざ使う理由が見当たらない。従って、今後も2D NANDを使い続けることが特策だが、NANDフラッシュメーカーは、生産ラインを急速に3D NAND用に振り替えており、DRAM同様、2D NANDも供給不足に陥るとの予想が広がっているのだ。

DRAMとNAND型フラッシュに代わるのが「SRAM/FRAM+NORフラッシュ」

このように、DRAMとNAND型フラッシュは、消費量の大きなコンピュータ市場の事情に押され変化しつつある。そうした中で、組み込み市場が必要とするDRAM、NANDフラッシュは、結果的になおざりにされ、技術進化が止まり、供給も不足するとの懸念が高くなっている。だからこそ、「産業機器をはじめとした組み込み機器も、メモリ構成を見直すべき時期が到来している――」のだ。

そこで、産業機器を中心にした組み込み機器の新たなメモリ構成として注目されているのが、SRAMやFRAMといったDRAMに比べ低容量のRAMと、NOR型フラッシュメモリ(以下、NORフラッシュ)の組み合わせだ。NANDフラッシュ内のプログラムを一度、大容量のRAM(DRAM)に展開して実行する「SnD(Store and Download)アーキテクチャ」ではなく、NORフラッシュから直接プログラムを読み込み、RAMは低容量で済ませるというアーキテクチャへの転換であり、SRAMからNANDフラッシュまで、あらゆる組み込み用メモリを手掛けるCypress Semiconductorなどが提唱している。

「SRAM/FRAM+NORフラッシュ構成」を採用する利点は、数多くある。

「SRAM/FRAM+NORフラッシュ」の魅力

まず、これらのメモリは、DRAMやNANDフラッシュと異なり、原則、組み込み用途向けに開発、供給されているため、産業機器分野などが求める長期供給、長期信頼性保証が成されているケースがほとんどだ。Cypressでも原則、105℃や125℃といった産業グレード、車載グレードの高信頼性製品をそろえ、10年程度の長期供給を実現している。

2つ目の利点は、RAMの不揮発化が図れ、DRAMでは実現できない価値を創出できる点だ。強誘電体を記録素子に使用するFRAMはご存じの通り、不揮発性メモリでありながら、揮発性RAM同様の書き換え速度を誇る。そのため、記憶保持のための電力供給が不要であり省電力化が実現でき、急な電源遮断でもデータを失わず、機器の信頼性向上にも貢献する。RAMとして使用する場合、書き込み回数が課題となるがCypressのF-RAM製品では、100兆回(1014回)とほぼ無限となっており、RAMとしての使用にほぼ問題はない。

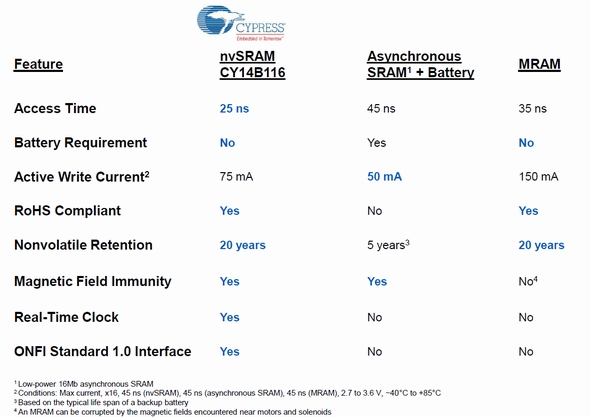

またF-RAM以外にも「nvSRAM」という不揮発性RAMの選択肢も存在する。nvSRAMとは、Cypress独自の不揮発性SRAMであり、一般的なSRAMに不揮発性のEEPROMを組み合わせたメモリ。動作状態では、SRAM領域を使用し、電源遮断時に、EEPROMにSRAMのデータを書き込み保持し、電源回復時にそのデータをSRAMに戻してくれるもの。F-RAM同様、バックアップ電源などの必要性がなくなる利点がある。

その他にも、NORフラッシュから直接プログラムが実行できることにより、高速起動が可能になることなども「SRAM/FRAM+NORフラッシュ構成」の利点として挙げられる。

微細化に余地、進化続くSRAM/FRAM+NORフラッシュ

このように組み込み領域にとって、利点の多い「SRAM/FRAM+NORフラッシュ構成」なのだが、“NORフラッシュは過去の技術であり、今後、技術進化が望めないのでは?”といった懸念を持つ方も多いだろう。それもそのはずで、NANDフラッシュの目覚ましい技術進化の陰で、NORフラッシュの進化は事実として滞りがちだった。しかし、3D化などNANDフラッシュの進化と、組み込み領域のニーズとの間で乖離(かいり)が目立ちつつある中で、再び、NORフラッシュの進化が加速しつつあるのだ。

NORフラッシュ最大手の旧SpansionとSRAM最大手の旧Cypressが合併して誕生したCypressでは、このほど、メモリ事業戦略を全面的に見直し、組み込み市場のニーズをこれまで以上に重視。先行きに不安を抱えるSnDアーキテクチャではなく、SRAM/FRAM+NORフラッシュ構成で組み込み機器の進化をサポートすべく、SRAM、FRAM、そしてNORフラッシュへの投資を継続的に強化していくことを決定。2016年から2017年にかけて、新製品を相次いで投入する方針だ。

NORフラッシュは高集積化&書き換え回数10倍アップへ

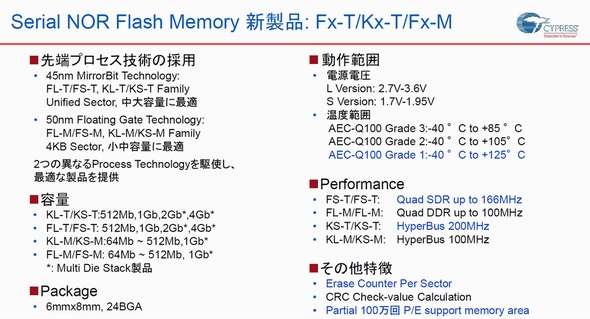

NORフラッシュでは、これまでの110nm、90nm、65nmプロセスから微細化を進展させた45/50nm世代品を2017年前半に投入する計画だ。

大容量に向くチャージトラップ技術「MirrorBit」採用NORフラッシュには45nmプロセスを、低容量に向くフローティングゲート(FG)技術採用NORフラッシュには50nmプロセスを採用し、低容量から大容量まで幅広く製品ラインアップを整える計画だ。45/50nmプロセス世代を選択した理由としては「市場要求のある容量のメモリを、最も高いコスト競争力で製造できるプロセス世代が、液浸露光工程がない45/50nm世代だったため」と説明する。

プロセス以外の技術進化も進む。その1つがインタフェースだ。現状、メモリインタフェースは、パラレルよりも信号数が少ないシリアルへの移行が進み、SPI、さらに高速なクアッドSPI、デュアルクアッドSPIの使用が定着してきた。ただ、こうしたSPIシリアルインタフェースの高速化は限界に達しており、新たな高速メモリインタフェースが求められている。

そこで、Cypressは独自のメモリインタフェースとして333Mバイト/秒の転送速度を誇る「HyperBus」を開発。HyperBus搭載NORフラッシュを「HyperFlash」として製品化し、高速起動や大容量転送が要求される車載インフォテイメント機器から採用が始まり、昨今では産業機器など幅広い組み込み用途へと普及しつつある。

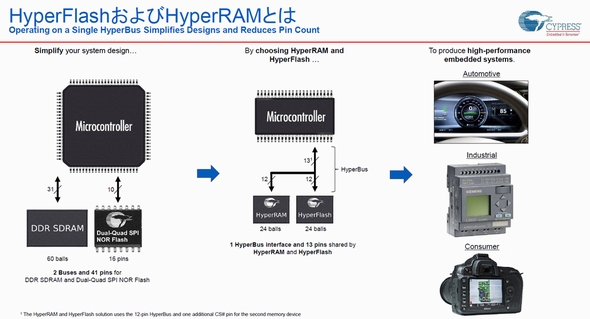

HyperBus対応製品として「HyperFlash」の他に「HyperRAM」も展開。メモリインタフェースを高速化できるだけでなく、HyperFlashとHyperRAMを併用することでメモリインタフェースに割く端子数を従来ソリューションに比べ大きく削減できるなどの利点もある (クリックで拡大)

またHyperBus対応のDRAM「HyperRAM」とHyperFlashをワンパッケージ化したメモリソリューションをこのほど製品化。従来のDDR SDRAMとデュアルクアッドSPIフラッシュ構成では、メモリインタフェースに合計41ピン必要だったが、HyperFlash+HyperRAMのマルチチップパッケージ(MCP)ソリューションであれば、13ピンで済む。これまでメモリインタフェースの制約から高価でサイズの大きなマイコンを使わざるを得なかった用途でも、低価格で小型な少ピンマイコンが使用できるなどの利点を提供する。

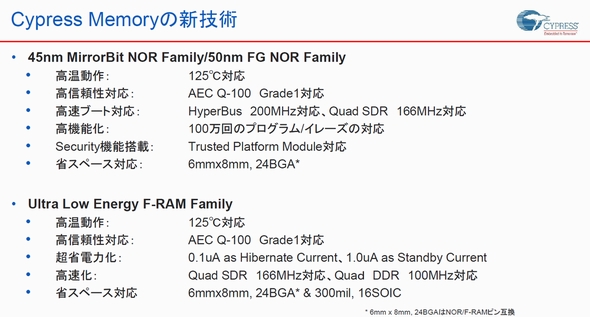

また新世代NORフラッシュ製品では、従来は10万回だった書き換え回数を10倍高め、100万回を実現するという。

「新世代品は、(プログラマブルSoCである)PSoC、マイコンの設計手法を応用し、インテリジェント機能をNORフラッシュに付加する。その1つが、セルごとの書き込み/消去回数を平準化インテリジェント機能で、書き込み/消去回数の大幅増加を実現した」と説明する。

「PSoCやマイコン製品に適用している機能ブロックごとに最適設計を行い融合させる開発手法を、メモリ製品にも適用しており、これまでよりも効率的に製品開発が実施できており、早期に製品ラインアップも整う見通し」とする。

MirrorBit品、FG品ともに、125℃/AEC Q-100グレード1対応の車載品質を備え、全ての製品は24ボールの6×8mmサイズBGAパッケージで提供する方針。インタフェースとしては、166MHz対応Quad SDRの他、MirrorBit品では200MHz対応のHyperBusを、FG品では、100MHz対応のQuad DDRを備えた製品をラインアップ予定で、ピン互換で豊富な選択肢が用意されることになりそうだ。

F-RAMはさらにローパワーに、nvSRAMは40nm世代品も

Cypressでは、F-RAMの新製品として、超低消費電力(ULE)版F-RAMを開発中で2017年からサンプル出荷を順次開始していく。同新製品は、新たに130nmプロセスを採用しハイバネート電流0.1μA、待機電流を1.0μAとそれぞれ従来品(180nmプロセス品)比10分の1以下にまで低減。「2032型ボタン電池を電源に、16バイトを20msのインターバルで書き換えを行った場合、電池寿命は競合比4倍の9,549日(26年間相当)持つ計算で、補聴器や電子棚札などバッテリー駆動の電池寿命を大幅に伸ばせることのできるメモリ」という。また微細プロセス採用の利点を生かし、大容量の16Mビット品も展開する。

SRAMについても、不揮発性SRAMである「nvSRAM」で、現行の110nm世代品の後継世代として、40nmプロセス品の開発に着手。「128Mビット品も実現できる見込み」とし、2018年からのサンプル出荷開始を予定しているという。

「産業機器などの組み込みシステムでのSnDアーキテクチャが限界を迎えつつある中、Cypressは、DRAMやNANDフラッシュに代わる組み込みメモリの開発をリードしていく。今後も継続的に、SRAM、FRAM、NORフラッシュなどのメモリに投資を行い、新技術を盛り込んだ新製品を安定的に、長期に、供給していく」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本サイプレス株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2016年12月31日