差異化技術を持つファウンドリとして、大手に対抗する三重富士通セミコンダクター:三重富士通セミコンダクター 取締役執行役員常務 千々岩雅弘氏

半導体受託製造専門企業(ファウンドリ)である三重富士通セミコンダクター(MIFS)は、「低消費電力」「組み込み不揮発性メモリ」「RF」の3つの領域で独自色の濃い差異化技術を構築し、大手ファウンドリに対抗する戦略を実践する。ファウンドリ3年目となる2017年は「差異化技術構築にメドが付き、国内外で積極的に受注を獲得する年」と位置付ける。同社取締役執行役員常務千々岩雅弘氏に、差異化技術の詳細や今後の事業戦略について聞いた。

発足初年度から想定を上回る業績を達成

――2014年12月の会社設立から2年が経過しました。これまでの業績を振り返ってください。

千々岩雅弘氏 三重富士通セミコンダクターは富士通セミコンダクター(FSL)の300mmウエハー対応生産拠点だった三重工場を母体に、ファウンドリ専門会社として発足した。実質的な発足初年度となった2016年3月期は、当初計画を大きく上回る売上高で、事業損益も黒字で終えられた。その結果、調査会社のガートナーが発表した2015年の世界ファウンドリランキングでも、前年より順位を上げ、8位にランクインすることができた。

2年目の今期、2017年3月期は、上期こそモバイル機器需要が当初想定を下回るなど売り上げ面で苦戦したが、下期に入り全般的に需要は回復傾向にある。上期の遅れを下期に挽回するよう努力を続けている最中だ。

――2016年は、40nmプロセス製造ラインの立ち上げに取り組まれました。

千々岩氏 総額100億円の出資(=出資比率約16%に相当)を受けている(台湾のファウンドリ企業である)UMC社の40nmプロセス技術と互換性のある40nmプロセス製造ラインを整備している。既に、月産3000枚(300mmウエハー換算)に対応するラインを整備し、一部顧客の特性確認も済み、エンジニアサンプルを製造、出荷している状況。2017年4~9月に量産が始まる見込みだ。

なお、40nmプロセス製造ラインは、近い将来の需要拡大に備え、月産5000枚を超える能力まで拡張できるように基盤を整えてあり、早期に拡張が可能だ。さらに、UMC社との互換性があるため、UMC社の製造ラインを使った増産対応が行えるフレキシビリティもある。

車載、IoT/ウェアラブルに向けた差異化技術

――あらためて、三重富士通セミコンダクターとしての事業方針、他のファウンドリとの差異化策をお聞かせください。

千々岩氏 大手のファウンドリに対し、生産規模や最先端微細プロセス技術ではなく、三重富士通セミコンダクター独自の差異化技術で対抗する戦略を発足以来、追求している。

差異化技術とは、低消費電力技術、組み込み不揮発性メモリ技術、高周波(RF)技術の3つだ。これら3つの技術をベースに、今後、需要拡大が見込まれる車載用半導体やIoT(モノのインターネット)/ウェアラブル端末用半導体を中心に製造受託を増やしていく方針だ。

低消費電力を実現する「DDC技術」

――差異化技術の開発状況を教えてください。

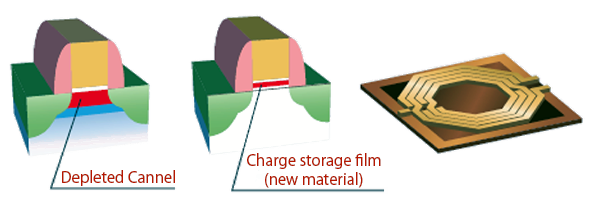

千々岩氏 まず、低消費電力技術については、FSL時代から手掛けているDDC(Deeply Depleted Channel)と呼ばれる超低消費電力CMOS技術の開発に継続して取り組んでいる。この技術は、トランジスタのしきい値(Vt)ばらつきを抑えて実効パフォーマンスを高めることが可能で、デバイスの電源電圧(VDD)を低減したニア/サブスレッショルド用途に適しており、リーク電流も抑制できる利点がある。

FSL時代には、55nmプロセスを用いて、VDD=0.9Vを実現したハイパフォーマンスイメージプロセッサを量産した実績もある技術だ。

ただ昨今は、競合ファウンドリ会社もVDD=0.9Vを実現する、いわゆる“Ultra Low Power(ULP)プロセス”を実用化しつつあり、単純にVDDだけで比較してしまうと、DDC技術の優位性が際立たなくなってしまった。そこで、VDD=0.5Vというさらにもう一段、VDDを下げられる技術へとブラッシュアップしているところだ。既に、進化版DDC技術を用いて、さまざまなデバイスを55nmプロセスで試作し、競合のULPプロセスよりも大きく消費電力を低減できることを確認している。2017年度中には、55nmプロセスによる量産品に採用される見込みだ。

40nmプロセスへのDDC技術適用についても、素子レベルの検証は終えており、55nmプロセスでの量産が始まり次第、本格的な開発に着手する。

ニーズに応える多様な組み込み不揮発性メモリ

――不揮発性メモリ技術の開発状況を教えてください。

千々岩氏 用途、ニーズに応じて、さまざまな組み込み不揮発性メモリ技術をそろえる方針で開発を進めている。

1つは、ロジック回路との親和性の高い不揮発性メモリとして、Plug-In Flashを自社開発している。Plug-In Flashは、ロジックプロセス互換でトランジスタ特性に影響を与えることなく製造できる他、追加工程数が少なく低コストという特長がある。今話題のウェアラブル端末やIoT端末などのコンシューマー向けに最適な組み込み不揮発性メモリであり、現在、40nmプロセスに導入できるよう開発を進めている。2016年度末までにマクロをリリースする予定である。

車載用途向けには、40nmプロセス対応不揮発性メモリを自社開発ではなく、標準的なサードパーティー製フラッシュメモリを使用してIP化を進めている。車載用組み込みフラッシュメモリの製造は、FSL時代から55nmプロセスで量産を行っており実績のある領域。そうした実績、ノウハウも生かし、40nm世代での受注獲得を目指していきたい。

ミリ波をCMOSで

――RF技術については、いかがですか。

千々岩氏 無線通信については規格ものであり、スタンダードなIPを取りそろえている。それに加えて、独自性のある技術/IPとして、富士通研究所と共同でミリ波帯のMMIC(Monolithic Microwave Integrated Circuit)をCMOS技術で製造する技術を構築した。現在、(半導体設計に必要な製造プロセスに依存した情報をまとめた)Process Design Kit(以下、PDK)を準備している。無線基地局の他、車載レーダー向けに対して、競争力のあるIPとして期待している。

――差異化技術がそろってきました。

千々岩氏 発足3年目を迎え、発足当初より取り組んできた差異化技術開発にメドが付いてきた。そういう意味でも、3年目の2017年は“第1フェーズの仕上げ”“刈り取りの時期”であり、新規商談獲得を積極的に図る1年になる。

より使い勝手の良い設計環境を整備

――新規商談獲得の成否の鍵を握る要素は、どの辺りにありますか。

千々岩氏 特長、競争力のある差異化技術/IPを開発、用意するだけでは、採用いただけない。差異化技術/IPは、これまでにない新技術だが、顧客側から見ると、これまでに使ったことのない未知の技術。簡単には使えず、採用にはハードルがある。

そこで、差異化技術による商談獲得の成否は、いかにPDK、ライブラリを要望に応じてカスタマイズできるか、使い勝手の良い設計環境を提供できるか、に掛かっている。

ライブラリのカスタマイズについては、われわれはこれまでIDM(垂直統合型半導体メーカー)として日々、設計と製造のすり合わせを行ってきた。そのため、設計側の要望を的確にくんでカスタマイズすることは得意だ。

ただ、そうしたカスタマイズ対応だけでは効率性が悪く、時間も掛かる。そこで、多くの要望に応えられる柔軟性のある設計環境の整備を急いでいる。具体的には、HiSIMを含めた複数のSPICEモデルに対応したPDKの用意や、大手ファウンドリのPDKから移行を支援するマイグレーションツールの整備、40nm車載向け(温度拡張)ライブラリなど、顧客要望の高いものは予め準備を行っているところだ。

国内での引き合いが増加

――営業活動も強化されますか。

千々岩氏 強化していく。当社の営業専門組織はなく、(販売代理店の)富士通エレクトロニクスと連携して、営業活動の強化に取り組んでいる。

これまでは、多くの顧客を抱える北米に重点を置いて営業活動を行ってきたが、今後は、中国をはじめとしたアジアへと広げている。

加えて、日本国内での提案強化に取り組んでいる。実は、これまでは日本国内では需要が少ないと思い海外に目を向けてきたのだが、国内半導体メーカーの生産体制見直しや、BCP(事業継続計画)の重要性の高まりから、ファウンドリ需要が生じ、引き合いが増えている。あらためて、国内市場の重要性を認識している。

――2017年は“第1フェーズの仕上げの年”という位置付けですが、第2フェーズでは、どのようなことに取り組む予定ですか。

千々岩氏 ファウンドリの従来型ビジネスモデルとは異なる、新しいビジネスモデルを構築していくことが目標になるだろう。

同時に、次の差異化技術の開発にも着手していく。その1つが、組み込み不揮発性RAMになるだろう。これまで開発してきた組み込み不揮発性メモリは全てROMだった。LSI、ICにとってRAMは重要な要素であり、将来的には不揮発性RAMが求められる。2016年にFSLと共にライセンス契約を結び共同開発に着手したNantero(ナンテロ)社のカーボンナノチューブ応用型不揮発性RAM「NRAM」も、第2フェーズに向けた技術の1つと言えるだろう。

2017年は、第2フェーズに向けて、さまざまな検討作業にも着手する。

開発エコシステムをさらに強化

――開発テーマが多岐にわたります。開発体制の強化策を教えてください。

千々岩氏 開発人員の強化を行っているが、効率の良い技術開発を行うため、パートナーとの連携を重視している。Nantero社とのNRAM開発や、富士通研究所とのミリ波対応MMIC開発などがその例であり、DDC技術でもスイスの民間非営利技術研究組織であるCentre Suisse d'Electronique et de Microtechnique(CSEM)と共同開発を実施している。今後も、タイムリーで必要な技術を補えるパートナーと手を組みながら、開発エコシステムを充実させていく。

そうした開発エコシステムの強化を狙い、IP開発を手掛ける開発拠点「高蔵寺事業所」(愛知県春日井市)を2017年3月に、名古屋市の中心部、名古屋駅前に移転する。より交通の便が良い立地になるため、お客さまやパートナー会社のエンジニアもより訪問しやすく、開発エコシステムの核になると期待している。

提供:三重富士通セミコンダクター株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2017年2月15日

Copyright © ITmedia, Inc. All Rights Reserved.