DC�Ւf��������֓����\�\�C���t�B�j�I�����uCoolSiC�v�u�����h����JFET�𓊓��FDC�O���b�h�̈��S����S��

�G�l���M�[���������Ȃ����d�^�z�d�ԂƂ��āA���ړx�����܂��Ă��钼���iDC�j�O���b�h�B���̎�����̃O���b�h�ł�DC�d���������ɍ����ɎՒf�ł��邩���d�v�ɂȂ�B�����ŋr���𗁂юn�߂Ă���̂��Y���P�C�f�iSiC�jJFET���B�Ȃ�SiC JFET��DC�d���Ւf�Ɍ����̂��BSiC�f�o�C�X�N��|����C���t�B�j�I�� �e�N�m���W�[�Y���������B

�����d���̎Ւf��SiC�����̂ɋr��

�@�J�[�{���j���[�g�����������ɂ����������ŁA���E�̓d�͎��v�͉E���オ��ő������Ă���B�Y�Ƌ@��s��œd�������d�������i��ł��邱�Ƃɉ����A����AI�̓o��ɂ����AI�Z�p�̕��y����C�ɉ������A�f�[�^�Z���^�[�̓d�͏���ʂ͋}�����Ă���B�ȃG�l�Ŕ��̋}�ƂȂ钆�ŁA���ړx�����܂��Ă���̂��A�����iDC�j�z�d�V�X�e���iDC�O���b�h�j���B

�@���݂̓d�̓V�X�e���ɂ́A�����ƌ𗬁iAC�j�����݂��Ă���B���d�������Ђ�ƒ�̃R���Z���g���o�āAPC��X�}�[�g�t�H���A���u��d�C�����ԂȂǂɓd�͂����������܂łɁA��������AC/DC�ϊ���DC/DC�ϊ����J��Ԃ����B�ϊ�������100���ł͂Ȃ����߁A�ϊ��̂��тɓd�͑�������������BDC�O���b�h�́A���̓d�͕ϊ����ł��邾�����炵�ADC�d���̂܂ܔz�d���āA���܂��܂ȕ��ׂɋ�������������B�ϊ��̉�����A���ꂾ���d�͑��������邱�ƂɂȂ�B

�@�����������ŋ��߂��Ă���̂��ADC�d���������ɎՒf����Ւf��iDC�Ւf�j���BDC�Ւf�ɂ����čł��傫�ȉۑ�̈�̓A�[�N�̔����ł���B�A�[�N����������ƁA�Ւf��̗�A�ړ_�̗n���Ȃǂɂ�鑹���������N�����B�ړ_���n������Ɠd�������ꑱ���Ă��܂���ɁA�ꍇ�ɂ���Ă͍�ƈ��Ɋ댯���y�ԉ\��������B���̂��߁ADC�d�����m���������ɎՒf���鑕�u���K�v�ɂȂ�B������DC�Ւf��Ƃ��Ē��ڂ���Ă���̂��A�����̂��B�����̂��g���ƍ�����DC�Ւf���\�ɂȂ邱�Ƃɉ����A���J�j�J�������[��q���[�Y�ȂǂƂ͈قȂ�A�@�B�I�Ȑړ_�������Ȃ��̂ŁADC�Ւf��̎����������Ȃ�B�C���t�B�j�I�� �e�N�m���W�[�Y �W���p���̓��X���R���́u���݂́A���J�j�J�������[��q���[�Y�ȂNj@�B���̎Ւf�킪���|�I�������߂Ă���B�d�͌n������藣���ꂽ�A����Ƃ������Ƃ�������₷���A��ނ��L�x�ň��������炾�B����DC�O���b�h�ł́A��荂���ɓd���̃I���I�t���X�C�b�`���O�ł��锼���̂��g��Ȃ���ADC�Ւf��Ƃ��Ă̗v�������Ȃ��B����܂Ŕ����̂�DC�Ւf��Ɏg���Ă��Ȃ������v�����v�Ɛ�������B

�@���������w�i�̉��A�C���t�B�j�I����DC�Ւf�p�r�̊g����������ĊJ�������̂��A�Y���P�C�f�iSiC�jJFET�A�uCoolSiC JFET�v���B

��I����R�Ō��낤�ADC�Ւf�Ɍ���SiC JFET

�@�����̂�DC�Ւf�ɗp����Ƃ����R���Z�v�g�͈ȑO����l�����Ă����B�������A�V���R���iSi�j�^SiC MOSFET�̓I����R�������̂ŎՒf���\���\���ł͂Ȃ��AMOSFET�̔��M���傫���̂ŕ��M����K�v�ɂȂ�B

�C���t�B�j�I�� �e�N�m���W�[�Y �W���p�� �C���_�X�g���A�����C���t���X�g���N�`���[���Ɩ{�� �}�[�P�e�B���O�� ���� ���X���R��

�@�����������ŁADC�Ւf�ւ̉��p�����҂���Ă���̂�SiC JFET���B��������SiC�́A�≏�j��d�E���x�������A�o���h�M���b�v���L���ȂǁA�����̂Ƃ��ėD�ꂽ���������BSiC��p�����p���[�����̂́ASi�p���[�����̂������ψ����ᑹ���ŁA�����X�C�b�`���O���\�ɂȂ�B���̂��߁A��d���A���d�������߂��鑾�z�����d�V�X�e���̃p���[�R���f�B�V���i�[��S���ԗ��̃C���o�[�^�[�Ȃǂł͑����i�K����AIGBT����SiC MOSFET�ւ̒u���������i��ł����B�C���t�B�j�I�������N�ɂ킽��A�uCoolSiC�v�̃u�����h��SiC MOSFET�Ȃǂ�W�J���Ă���B�����č���ACoolSiC�Ƃ��Ă͏��ƂȂ�SiC JFET�𓊓�����B

�@�u�C���t�B�j�I����SiC MOSFET�N���A���z���A�ԍڃC���o�[�^�[�Ƃ��������܂��܂ȃA�v���P�[�V�����Ŏg�p����Ă��邪�A��{�̓X�C�b�`���O�p�r�ɂȂ�BCoolSiC JFET�́A�����[��T�[�L�b�g�u���[�J�[�ȂǁA��{�I�ɂ�DC�̎Ւf�Ƃ����p�r��z�肵�Ă���v�i���X���j

�@���X���́ADC�̎Ւf�ł�MOSFET�ł͂Ȃ�JFET�̕����K���Ă���Ƌ�������BJFET�̓I����R���Ⴍ�A���낤�ȃf�o�C�X�����炾�B

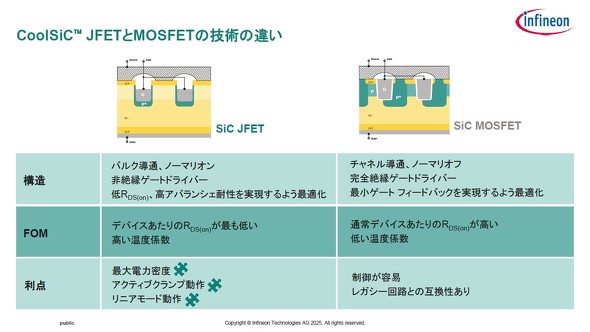

�@JFET�́A�ڍ��^�d�E���ʃg�����W�X�^�iJunction Field Effect Transistor�j�̖��������ʂ�A�����̂�ڍ����č��FET�ł���BN�^JFET�̏ꍇ�AN�^�����̂�y��Ƃ��ăQ�[�g�����ɃE�F�����`�����AP�^�����̂ߍ����PN�ڍ������B�\�[�X�ƃh���C��������P�^�^N�^�����̂ߍ��݁A�Q�[�g�����̒����Ɏ_���������MOSFET�ɔ�ׂĒP���ȍ\���ɂȂ��Ă���B���̃V���v���ȍ\���ɂ���āA��I����R�⌘�낤���Ƃ�����JFET�Ȃ�ł͂̃����b�g�����܂��B

�C���t�B�j�I�� �e�N�m���W�[�Y �W���p�� �C���_�X�g���A�����C���t���X�g���N�`���[���Ɩ{�� �t�B�[���h�A�v���P�[�V�����G���W�j�A�����O�� �v�����V�p���G���W�j�A ���Q��

�@JFET�ł́A�h���C������\�[�X�Ƀo���N�������ēd���������B�����MOSFET�́AMOS���ӂɌ`�����ꂽ�`���l����ʂ��ēd���������B���̂��߁AMOSFET�͂ǂ����Ă��`���l����R�������傫���Ȃ�A�I����R�����������邱�Ƃ�����B�u�����_�̃e�N�m���W�[�ł́ASi MOSFET��SiC MOSFET�ɔ�ׂāASiC JFET�̕����͂邩�ɃI����R�̒Ⴂ�f�o�C�X������v�Ɠ��X���͐�������B

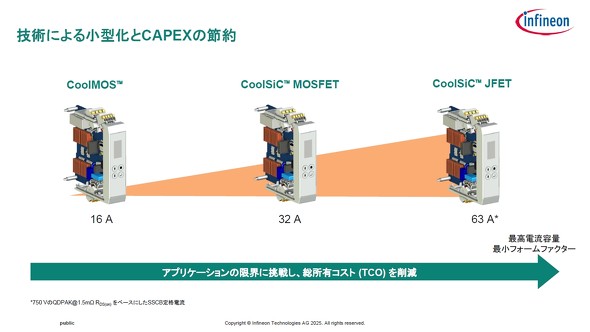

�@�C���t�B�j�I�� �e�N�m���W�[�Y �W���p���̗��Q��iLi Kyongyul�j���́uSiC JFET�͈�ʓI��SiC MOSFET���35�����x�A��R�������������v�Ɛ�������B�I����R���������Ȃ邱�ƂŁA�����t�H�[���t�@�N�^�[�Ń����[���\�������ۂɈ�����d�����啝�ɑ�����B�uSi MOSFET�ł͕��דd����16A���������̂��ASiC MOSFET���̗p�����2�{��32A�ɂȂ�ASiC JFET���̗p����ƁA����ɖ�2�{��63A�܂ő�����v�i�����j�B����͐ݔ�������̒ጸ�ɑ傫���v�����邾�낤�B

�@����ɁAJFET�̓��j�A�̈�Ŏg���邱�Ƃɉ����A�A�o�����V�F�ϗʂ����ɑ傫���B������AJFET�����\���ʂł̓����ɂȂ�B�u�f�o�C�X�̎ア�����́A��{�I�Ɏ_�������ӂɑ��݂���BJFET�̏ꍇ�A���������_���������݂��Ȃ��̂ŃA�o�����V�F�ϗʂ��傫���B�����JFET�̑傫�ȓ������v�i���X���j�BMOSFET�́A�d�����W�����ċǏ��I�ɔM���Ȃ�z�b�g�X�|�b�g����������ȂǁA���S����̈�iSOA�j�������Ȃ�P�[�X������BJFET�͍\���I�Ƀz�b�g�X�|�b�g���ł��Ȃ��̂�SOA�͍L���B�܂�AJFET�͍\���I��MOSFET�������ɂ����̂��B

�@�����́uSiC MOSFET���A�o�����V�F�ϗʂ͔����Ă��邪�A��{�I�ɂ͍ő��i�d���܂ł͈̔͂ł����g�p�𐄏����Ă��Ȃ��v�ƕt��������B���̂��߁A�T�[�W�d������SiC MOSFET��ی삷�邽�߂ɁAMOV�i���^���_���o���X�^�j��TVS�i�ߓd���}���j�_�C�I�[�h�A�X�i�o��H�Ȃǂ�lj�����K�v������̂ŕ��i�_���������Ȃ�B�����SiC JFET�̏ꍇ�́A�A�o�����V�F���[�h��{�i�I�Ɏg�p�ł���ƒ�Ă��Ă���Ɨ����͏q�ׂ�B

SiC JFET�{MOSFET�̃J�X�R�[�h�\���Łu�m�[�}���[�I�t�v��

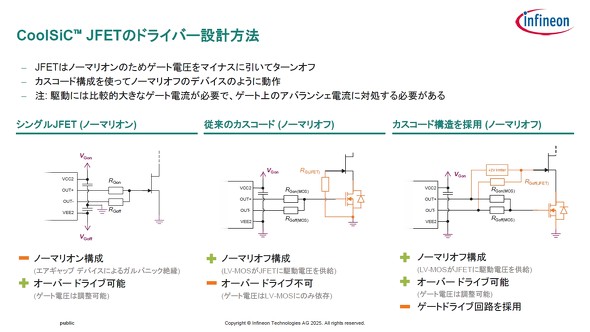

�@����ŁAJFET�͂�∵���ɂ����_������B���ꂪ�m�[�}���[�I�����BJFET�ł́AP�^�����̂�N�^�����̂̋��E�ʂŃz�[���Ɠd�q���������A��R�w��������B�Q�[�g�d�����������ƁA���̋�R�w���L�����ă`���l�����ӂ����A�h���C���d�����Ւf����B�܂�A�Q�[�g�d���������Ă��Ȃ���Ԃł͏�Ƀh���C���d���������̂ŁAJFET�̓m�[�}���[�I�������������Ă��邱�ƂɂȂ�B�u�G���W�j�A���g������Ă���̂́A��͂�MOSFET�̂悤�ɁA�Q�[�g�d����0V�̂Ƃ��ɂ̓h���C���d��������Ȃ��m�[�}���[�I�t�̃f�o�C�X���B�X�C�b�`���O��������₷���v�Ɠ��X���͏q�ׂ�B

�@����ɂ��ẮASiC JFET�ƒ�ψ�MOSFET�iLVMOS�j���J�X�R�[�h�ڑ����邱�ƂŁA�m�[�}���[�I�t�̉�H���\���ł���B��̓I�ɂ́ASiC JFET�̃\�[�X�[��LVMOS��ڑ����ALVMOS�̃\�[�X�[�̓O���E���h�ɐڑ�������ŁASiC JFET�̃Q�[�g��LVMOS�̃\�[�X�[�ɂȂ��B����ɂ��A��H�̓m�[�}���[�I�t�ɂȂ�B�uDC�Ւf�̃A�v���P�[�V�����ł́A��{�I�ɂ̓m�[�}���[�I�t���D�܂��B�ŋ߂�LVMOS�̓I����R��0.4m����0.5m���ȂǁA���ɒႢ���i�������B���̂悤��LVMOS��SiC JFET��g�ݍ��킹��A�e�ՂɃm�[�}���[�I�t�������ł���v�i�����j

�@�C���t�B�j�I���́A�m�[�}���[�I�t���ێ����A��R����������ɉ�������uAdapted cascode�v�\������Ă���BAdapted cascode�ł́A1�̃Q�[�g�h���C�o�ŁALVMOS�𐧌䂵�Ȃ���ASiC JFET�ɂ��{2V������ł���悤�ɂ��Ă���BSiC JFET�̃Q�[�g�ɐ��d�����������ƁA��R����������ɉ����邩�炾�B�u�{2V��������ƁA�I����R���15���ጸ�ł���v�i�����j

SiC JFET���m�[�}���[�I�t�Ŏg�����߂̉�H�\���B�E��2�̐}�ł��J�X�R�[�h�\���ŁA�m�[�}���[�I�t�Ƃ��Ďg����@�F�C���t�B�j�I�� �e�N�m���W�[�Y �W���p��

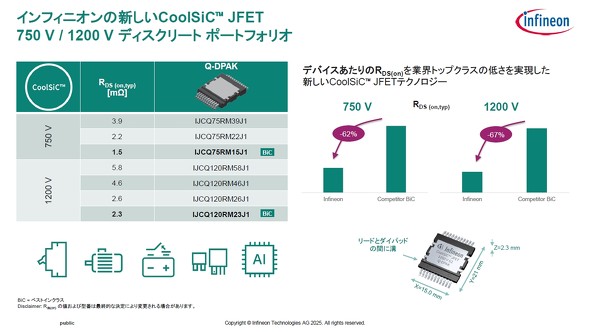

�@�C���t�B�j�I���͌��݁A��1�����CoolSiC JFET�̃T���v�����o�ג����B�ʎY�J�n��2026�N��\�肷��B��i�d����750V��1200V��2��ނŁA�I����R�̍ŏ��l��750V�i�ł�1.5m���A1200V�i�ł�2.3m���Ɣ��ɒႢ�B�u���J�j�J�������[���̓I����R���܂��������̂́ACoolSiC JFET�����ڑ����Ďg���I����R�͔����Ɍ���B2.3m����2����Ŏg���ƁA�I����R��1.15m���ɂȂ�Ƃ���������v�i�����j������i�ł̓I����R������ɒႢ�i����p�ӂ���\�肾�B

�@�p�b�P�[�W�ɂ�Q-DPAK���̗p����B���̃p�b�P�[�W�ł͕Б��ɕ��Ԓ[�q���S�ăh���C���[�q�ŁA���Α��ɕ��Ԓ[�q�̂قƂ�ǂ��\�[�X�[�q�ɂȂ��Ă���B�u�����̒[�q��ʂ��ēd��������邱�ƂɂȂ�̂ŁA�����ł���R�ᕪ�����点��B������SiC MOSFET�ł�3�[�q�p�b�P�[�W�����p����邪�A���̃p�b�P�[�W���Ɠd��������郋�[�g���ׂ��Ȃ�̂Œ�R�������ł��Ȃ��Ȃ�v�i�����j�B����ɁAQ-DPAK�̏�ʂɂ̓t���[�����ނ��o���ɂȂ��Ă��āA���M�ڎ��t������B���̂��ߕ��M�������コ������B���݂�Q-DPAK�݂̂����A����̓p�b�P�[�W�̎�ނ����₵�Ă����B

�@�ψ�1200V��CoolSiC JFET�𓋍ڂ����]���{�[�h���p�ӂ��Ă���B�m�[�}���[�I���A�m�[�}���[�I�t�����̃g�|���W�[������ALVMOS��J�X�R�[�h�\���p�̃Q�[�g�h���C�oIC�̓C���t�B�j�I�������g�p���Ă���B

�@�����́uDC�d�����Ƃɂ��������ɎՒf�������Ƃ����v���������B�����������ŁA���J�j�J�������[��q���[�Y�Ȃǂɉ����āASiC JFET�Ƃ����I���������邱�Ƃ�m���Ă��炢�����v�ƌ��B�ߔN�ł̓��[�^�[�̃u���[�J�[�Ƃ��āASiC JFET���g�������Ƃ����v�]�������Ă����Ƃ����BSiC�p���[�����̂̕���ł͒��炭�ASiC SBD�i�V���b�g�L�[�o���A�_�C�I�[�h�j��SiC MOSFET�����ڂ𗁂тĂ����B�����SiC JFET��DC�Ւf�Ƃ����A�v���P�[�V�����ŁA���̐��\�����悤�Ƃ��Ă���B�C���t�B�j�I���͂��̃g�����h����������Ƒ����ACoolSiC JFET�̐��i�Q���g�[���Ă����B

Copyright © ITmedia, Inc. All Rights Reserved.

�֘A�����N

�F�C���t�B�j�I�� �e�N�m���W�[�Y �W���p���������

�A�C�e�B���f�B�A�c�Ɗ��^����FEE Times Japan �ҏW���^�f�ړ��e�L�������F2025�N10��24��