モバイルDRAMの省電力に新機能、ディープパワーダウンとセルフリフレッシュモードが融合:低データレートでの消費電力を劇的に低減

スマートフォンなどモバイル機器の多くは、待機状態の割合が長く、待機時の消費電力削減が重要です。モバイル機器に搭載されるDRAM(モバイルDRAM)も低データレートでの消費電力削減が求められています。そうした中で、ウィンボンドは、低データレートで動作するモバイルDRAMの消費電力を劇的に低減させる新機能を開発しました。

今日、携帯電話はどこへ行くにも持ち運ばれ、一日中手放せないデバイスです。しかし、ほとんどの時間が待機状態であるのも事実です。常に電源をオンにしながらも、積極的に使用しない状態が多いでしょう。つまり携帯電話はポケットの中やデスクの上、ベッドサイドで、アプリ起動やビデオストリーム視聴を待ち続けているのです。

これは、携帯電話のアプリケーションプロセッサ負荷サイクルは非常に低い動作レベルが長時間に及ぶことを意味し、ゆっくり動作していた操作システムや無線デバイスは急な負荷の重い短期動作によって中断されます。アプリケーションプロセッサをサポートする低電力DRAMメインメモリでも同じパターンが観測される可能性があり、ほとんどの時間は低データレートで動作するのに費やされますが、プロセッサへのデータレートの高速転送は短期間です。

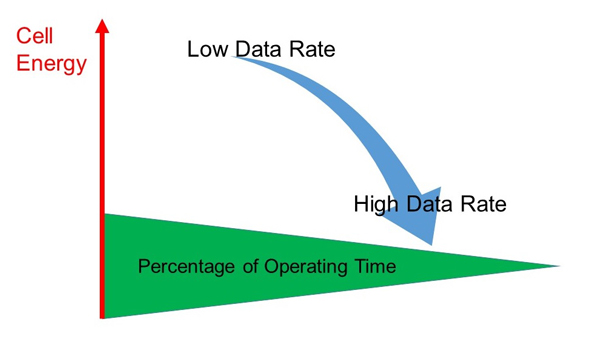

DRAMデバイスの業界標準ではまさに、少量データ転送時に未使用のメモリアレイ部分のデータがリフレッシュされてしまうことを回避するため用いられる、省電力機能のPASR(Partial Array Self-Refresh)が定義されています。それでもモバイルDRAMデバイスで消費されるエネルギーの大部分は、通常、低データレートで使用されます。これは、モバイルDRAMがこのような低データレートで動作する時間が非常に長いためです(図1参照)。

図1:モバイルDRAMは、高データレートよりも低データレートにて消費する電力(ワット)が低いにもかかわらず、低データレートでの動作が、消費される総エネルギーの大部分を占めます。 (画像クレジット:ウィンボンド)

これは、モバイルDRAMが低データレートでの動作時に消費電力を削減できることを意味し、非常に大きなメリットであるといえます。ウィンボンドは、低データレートで動作するモバイルDRAMの消費電力を劇的に低減させる新機能を開発しました。

標準的なDRAMの省電力機能

DRAMのJEDEC規格では、ATCSR(Auto Temperature Compensated Self Refresh/自動温度補償セルフリフレッシュ)、設定可能なドライブ強度、PASR(パーシャルアレイセルフリフレッシュ)などの省電力機能が規定されています。これらの機能は、JEDECで定義されているEMRS(Extended Mode Register Set/拡張モード・レジスタ・セット)で規定されている命令を実行することによって導入できます。PASR機能は、データレートが低い場合に適用されます。これは、DRAMとアプリケーションプロセッサ間のデータ転送速度が低く、使用されているすべてのデータがメモリセルの特定バンクに保持されるという原則に基づいて動作します。これは、残りのバンクを未使用データのためにリフレッシュすることで消費される電力を節約することを可能にします。

典型的な携帯電話の使用環境では、常時使用されているオペレーティングシステムコードは、標準的な256MビットDRAMの1つのバンクに格納され、アプリケーションデータに利用される他の複数バンクは、アプリケーション未使用時にリフレッシュされる必要がありません。PASRが作動している間、DRAM内部のすべての内部電圧ジェネレータは低電力モードのままです。

PASRの操作では、オペレーティングシステムコードなどの常時稼働データを、定期的に必要とされるアプリケーションデータのような他のデータタイプから慎重にパーティショニングする必要がある点も重要です。

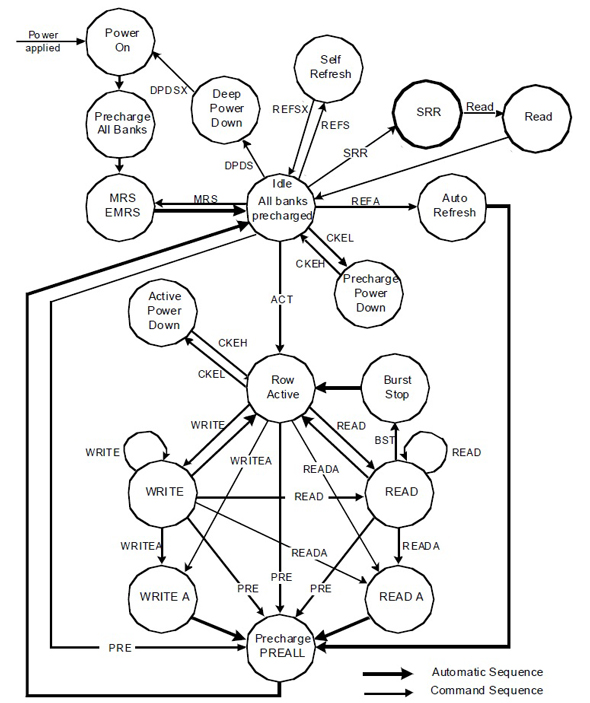

これとは別に、JEDEC規格では、メモリアレイ全体がシャットダウンするDPD(ディープパワーダウン)モードが定義されています。MRS(モードレジスタセット)とEMRS内の全情報と同様に、デバイス内部のすべての内部電圧ジェネレータが停止し、すべてのデータが失われます。DPDからアクティブモードに移行すると、完全な再初期化プロセスを実行する必要があります(図2参照)。これはメモリ操作のレイテンシーに影響を与えます。再初期化により、メモリバッファのアプリケーションプロセッサからの呼び出しとバッファが使用可能になるまでの間に遅延が発生します。

ウィンボンドの新しい拡張PASRモード

PASRモードによる省電力は便利である反面、制限があります。そこで、ウィンボンドはJEDEC規格にとらわれない、新たなDSR(ディープセルリフレッシュ)モードを実装することにより、PASRを超える省電力方法をご提案しています。

DSRは、低データレートでPASRと同じように動作し、使用中データを1つまたは複数のバンクに割り当て、その中でデータをリフレッシュし、他の残りのバンクはリフレッシュ動作を停止、電流を止めて、データを失ってもよいようにします。PASRモードとの相違は、メモリセルの未使用バンクがDPDモード状態になることです(図3参照)。

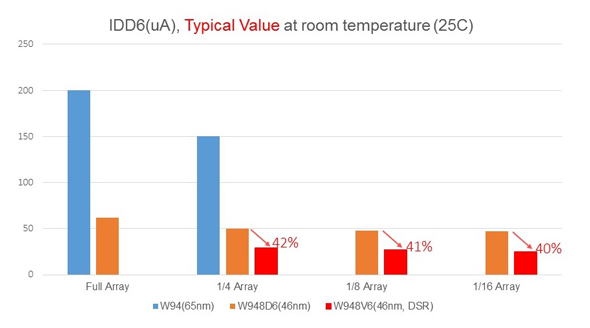

これは、セルフリフレッシュモードで使用される総エネルギーを削減するという利点があり、PASRモード自体よりもさらに省電力です(図4参照)。この図では、ウィンボンドのW948D6デバイスの典型的なPASRモード電流を示しています。最新の46nmプロセスで製造されたW948D6は、フルアレイがセルフリフレッシュ(IDD6)モードにあるときの消費電力と比べて、標準のPASRモードにて適度な節電を実現します。W948D6は新しいDSRモードを提供していませんが、46nmのW948V6はDSRモード対応です。グラフの赤いブロックは、PASRモードの動作に比べて電力が40%以上低下することを示しています。

新しいDSRモードはJEDEC仕様と互換性があり、EMRSへの(標準外の)追加定義のみ必要としています。DSR機能を追加することによるユーザーのハードウェア設計や、標準のJEDECピン配置に変更はありません。設計者は、基板レイアウトを変更せず、メモリコントローラに簡単な追加定義を実装することで、以前のDRAMからW948V6などのDSR対応DRAMに移行することができます。

前述のように、DPDから復帰するためには、メモリバンクを完全に再初期化する必要があります(図5参照)。これは、PASRモードからアクティブモードへの切り替えに比べて、DSRからアクティブモードへの切り替え時のレイテンシーの方が長いことを意味します。

DSR機能展開に向けてのロードマップ

ウィンボンドのロードマップでは、すでに量産中の256Mビット W948V6KBHXシリーズに加えて、今後数カ月にわたり多くのLPDDRデバイスにDSR機能が導入されていきます。DSR機能を備えた新しいデバイスとして、2018年前半に32MビットのPseudo-SRAM(PSRAM)、さらに2018年後半に2Gビット1.8V / 1.2V LPDDR2 DRAMを発売する予定です。

DSRオプション装備のこれら新製品により、携帯電話やその他のバッテリ駆動デバイスメーカーは、DRAM起因の総エネルギー使用量を削減し、低データ転送速度作動時のさらなる電力節約が可能になります。

【著:ウィンボンドエレクトロニクス/Hsiu-Min, Lin(DRAMプロダクトマーケティングマネージャー)】

Copyright © ITmedia, Inc. All Rights Reserved.

提供:ウィンボンド・エレクトロニクス株式会社

アイティメディア営業企画/制作:EE Times Japan 編集部/掲載内容有効期限:2018年12月13日