ボードの電源系雑音、最適設計で解決:実装技術 パワーインテグリティ(2/3 ページ)

ボードの電源/グラウンド・プレーンが揺れている。ボードに載せる半導体チップの高速化が原因だ。さまざまな電子機器において、電源/グラウンドはもはや理想的な一定電位とは見なせない。それどころか、雑音の伝搬/放射経路として扱う必要がある。この雑音の影響を抑えるためには、電源回路と半導体チップをつなぐ電源分配回路の全体にわたる最適設計が不可欠だ。

第1部 電源系の広帯域/低インピーダンス化、新型部品やEDAツールで対応急ぐ

「コンデンサの等価直列抵抗(ESR)は、低ければ低い方が良い」というこれまでの常識が覆されつつある。確かにコンデンサは一般に、ESRが低いほど高性能だとされる。電気的な特性が理想的なコンデンサに近付くからだ。このような特性を備えるコンデンサを使えば、例えば無線信号処理回路においてQ値の高いフィルタを実現でき、妨害波の影響を除去しやすく、希望波を高い品質で取り出せる。電源系雑音の影響を抑える目的でボードの電源/グラウンド間に挿入するコンデンサ(デカップリング・コンデンサ)も、これまでESRは低い方が望ましいとされてきた。

ところが今、この考え方に変化が生じている。「コンデンサ単体のESRが低過ぎると、電源系雑音の影響を増大させてしまう危険性がある。適切な値に調整すべきだ」(米Sun Microsystems社のシニア・シグナル・インテグリティ・スタッフ・エンジニアで電源分配回路の研究者として著名なIstvan Novak氏)というのである。

こうした新しい考え方を導入する必要が生じたのは、電源系雑音の影響が今までになく大きくなっているからである。一体、ボードに何が起きているのか。背景は何か。そして対応策は。第1部では、新たな局面を迎えたパワー・インテグリティを解説する。

高速デジタルLSIが元凶

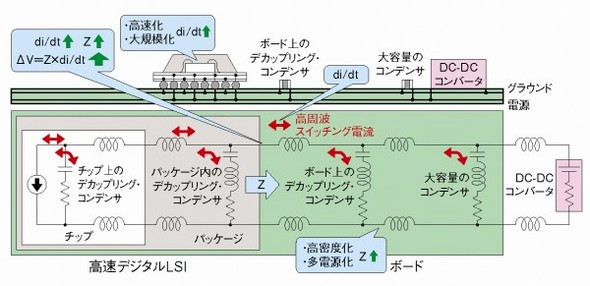

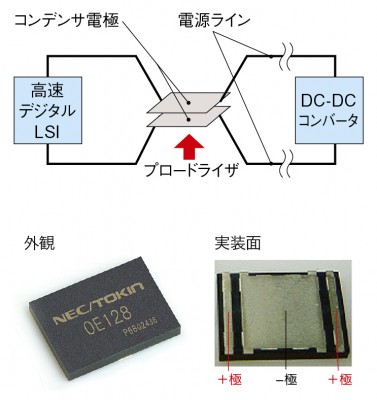

電源系雑音の問題を困難にしている元凶は、ボードに搭載する高速動作の大規模デジタルLSIにほかならない(図1)。具体的には、マイクロプロセッサやグラフィックス・プロセッサ、ハイエンドのFPGAやDSPなどである。

図1 電源分配回路の品質確保が困難に 電源回路(DC-DCコンバータ)とデジタルLSIをつなぐ電源分配回路の模式図である。電子機器の心臓部であるデジタルLSIの高速/大規模化に伴って、電源系雑音の影響が大きくなる。

これらのデジタルLSIに集積したCMOS回路が高速にスイッチングすると、ボード上の電源回路(DC-DCコンバータ)とその負荷であるデジタルLSI自体をつなぐ電源分配回路に高周波電流が流れて、雑音を発生させてしまう。

この電源系雑音の大きさは、デジタルLSIから見た電源分配回路のインピーダンス(Z)に高周波スイッチング電流の時間的変化量(di/dt)を乗じた値になる。この原則そのものは従来から変わらない。問題は、最近になってdi/dtが大きくなってきたことだ。半導体プロセス技術の微細化を原動力に、デジタルLSIが高速化と大規模化を続けているからである。プロセッサのコア回路ではGHzの領域に、メモリー・インタフェース回路では数百MHzに達した*1)。

一方で集積規模の拡大による消費電力の増加を抑えるべく、電源電圧は低下の一途をたどる。コア回路では1Vを切った。この結果、消費電流は増大傾向にある。つまり、デジタルLSIの高速スイッチング動作で発生する高周波電流の変化速度と振幅の両方が大きくなっている。

こうしてdi/dtが増大し、電源系雑音が大きくなる。しかも悪いことに、デジタルLSI自体は前述の通り電源電圧が低下しており、電源電圧の誤差に対する許容度(マージン)は小さくなっている。電源系雑音に対する耐性は低下する一方だ。従来は問題にならなかった大きさの雑音が、動作不良の原因になり得る*2)。

悪い条件はこれだけではない。電源電圧が異なる複数のデジタルLSIを搭載することも、ボードの電源系雑音を大きくしてしまう。しかも、あらゆる電子機器で小型化が進み、ボードの実装面積は削減される傾向にある。つまり、ボードに理想的な形状の電源/グラウンド・プレーンを用意することが難しくなっている。電源分配回路のインピーダンスが高まって、電源系雑音を増加させてしまう。まさに踏んだりけったりの状況である。

EMIや信号品質にも影響

電源系雑音の影響はデジタルLSIの動作不良だけにとどまらない。第1に、EMIの原因になる。ボードの電源プレーンとグラウンド・プレーンが共振(いわゆるプレーン共振)することで平行平板型のパッチ・アンテナとして機能し、雑音を空間に放射してしまうのだ。

第2に、入出力回路のシグナル・インテグリティ(伝送信号の品質)を劣化させてしまう。デジタルLSIの電源やグラウンドの電位が雑音によって変動すると、インタフェース回路にクロック信号を供給する回路の動作しきい値が揺らぐ。すると伝送信号の論理レベルの遷移タイミングがずれる。こうして、伝送信号のジッターが増大する。

電源系雑音に直面する機器が拡大傾向にあることも、ここ最近の傾向といえるだろう。かつて電源系雑音の問題は主に、サーバー機や通信インフラ装置などのハイエンド・ボードに限られていた。低電圧/大電流動作という、電源系雑音の影響が大きくなりやすい高性能プロセッサを採用していたのがこれらのボードだけだったからだ。

しかし現在では、民生機器に搭載するデジタルLSIも高速化が進んでいる。加えて、「デジタル家電やパソコンでDDR2対応メモリーの採用が本格的に始まった。こうした機器では、メモリー・インタフェースの同時スイッチング雑音に起因する電源系雑音の対策に、相当苦労しているようだ」(アンソフト・ジャパンでSIプロダクト担当のマーケティング マネージャーを務める渡辺亨氏)。

さらに、「デジタル映像信号向けインタフェース規格であるHDMI(High Definition Multimedia Interface)の導入によって、一般的な民生機器でも電源系雑音の問題が顕在化した」(パナソニック エレクトロニックデバイスのマーケティング本部 デバイスアプリケーションセンター FAEグループでチームリーダーを務める西山公治氏)とする指摘もある。「電源系雑音が、映像の劣化として機器のエンド・ユーザーの視覚に飛び込んでしまうようになった」(同氏)。

「ある車載オーディオ機器では、FM放送波の周波数帯域に電源系雑音が重畳し、受信音声が途切れてしまった」(EMC関連のコンサルティングなどを手掛けるシステムデザイン研究所で代表取締役を務める久保寺忠氏)という事例もある。

こうした民生機器の開発では、ハイエンド機器のボードに比べて対策に費やせるコストに制約があるほか、設計現場に対策技術の蓄積が比較的少ないことなどが、電源系雑音問題の解決をさらに難しくしているようだ。

対策部品の進化が始まる

電源系雑音へのボード上での対策は、電源分配回路のインピーダンスを低く抑えることに尽きる。先に述べた通り、雑音の大きさはインピーダンス(Z)に高周波スイッチング電流の時間的変化量(di/dt)を乗じた値になるからだ。ボード設計者がdi/dtを制御することは現実的ではない。従って、実際にはインピーダンスの低減が唯一の解になる。

最も一般的な対策方法は、デカップリング・コンデンサを使うことである。電源とグラウンドの間にコンデンサを挿入することで、高周波スイッチング電流に対する低インピーダンス経路を形成し、デジタルLSIのスイッチング動作で生じる高周波電流をグラウンドに流し込む。こうすれば、デジタルLSIの高周波電流が電源分配回路を介してボード上に拡散したり、空間に放射されることを防げる。

そのためには、電源系雑音を問題ない大きさに抑えられるインピーダンスの目標値(いわゆるターゲット・インピーダンス)を設定し、これを達成するようにコンデンサの品種や搭載位置、搭載個数などを最適化するといった作業が必要だ(第2部「電源分配の最適化技術を開発、最小コストで高い品質を実現」を参照)。

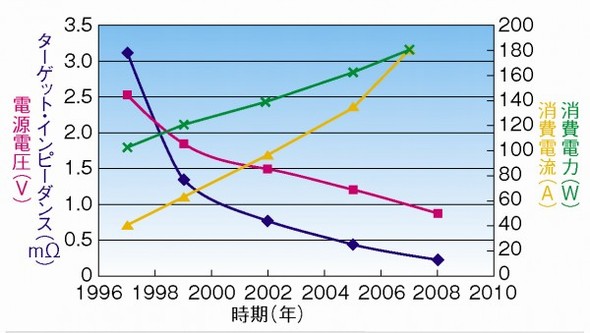

しかし実際には、コンデンサの最適配置という旧来の対策技術だけで解決することは難しい。デジタルLSIの高速化に伴って、広い周波数帯域幅にわたって、インピーダンスを極めて低く抑えることが求められているからである(図2)。

図2 インピーダンス目標値の低下が続く マイクロプロセッサが電源分配回路に求めるインピーダンスである。微細化の進展に伴って電源電圧が低下する一方、消費電力は増加する傾向だ。従って消費電流は増える。この低電圧/大電流のマイクロプロセッサに供給する電源電圧の誤差を抑えるには、インピーダンスを引き下げなければならない。出典:ITRS(International Technology Roadmap for Semiconductors)の資料を基に米Ansoft社が作成

そこで、電源分配回路の「広帯域/低インピーダンス化」を目指し、対策部品が進化を始めた。具体的にはESR調整品や広い周波数帯域にわたって低いインピーダンスを得られる品種などが出てきた。「高速インタフェースが一般化し、問題になる雑音の周波数は高まる一方だ。この動向に既存のデカップリング・コンデンサが追いつかなくなってきた。これがさまざまな新型部品が登場している背景である」(芝浦工業大学 工学部電子工学科 教授の須藤俊夫氏)。以下に、その一部を紹介しよう。

コンデンサのESRを調整

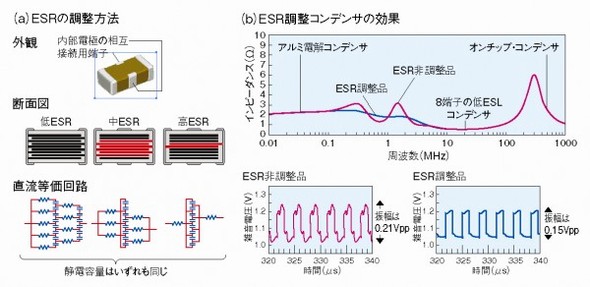

最初に紹介するのは、冒頭で述べた「コンデンサ単体のESRが低過ぎると、電源系雑音の影響を増大させる危険性がある」という考え方に基づいて、ESRの値を調整したコンデンサである。「ESR調整コンデンサ(Controlled ESR Capacitor)」と呼ぶ*3)。すでに国内の電子部品メーカーが供給を始めている。

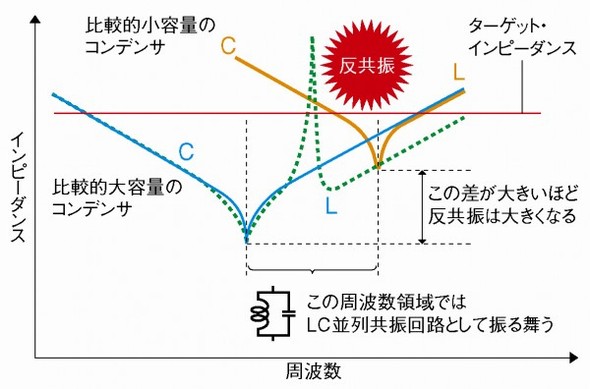

ESRの調整が必要になる理由はこうだ(図3)。ボード上の電源分配回路は通常、Al(アルミ)電解コンデンサやタンタル・コンデンサ、セラミック・コンデンサなど、静電容量や寄生成分の大きさが異なる複数のコンデンサを組み合わせることで広帯域/低インピーダンス化を図る。1つのコンデンサが低インピーダンス経路として機能するのは、寄生成分であるESRと等価直列インダクタンス(ESL)の影響によって、比較的狭い周波数範囲に限られるからだ。

図3 コンデンサの並列接続で反共振が発生 電源分配回路のデカップリングに使うコンデンサは、必ずしも等価直列抵抗(ESR)が低ければ良いというわけではない。品種が異なる複数のコンデンサを組み合わせた際に反共振が発生し、インピーダンス特性に大きなピークが生じる可能性があるからだ。反共振が発生するのは、品種が異なる2つのコンデンサによって、特定の周波数領域で「等価的」にLC並列共振回路が形成されるためである。この図では、「比較的大容量のコンデンサのL成分」と「比較的小容量のコンデンサのC成分」によってLC並列共振回路が形成され、その並列共振周波数は1/[2π・√(L・C)]になる。

具体的には、周波数が自己共振周波数(SRF)を下回る領域ではコンデンサ、SRFを超える領域ではインダクタとして振る舞う。このためコンデンサのインピーダンス特性はV字型になる。ESRによってこのV字の頂点部分の鋭さ、つまり共振の鋭さに相当するQ値が決まるわけだ。ESRが低ければQ値は高くなり、ESRが高ければQ値は低くなる。

ところが、電源分配回路にSRFが異なる複数のコンデンサを接続すると、並列共振回路が構成されてしまう。この結果、2つのSRFの間の周波数で、電源分配回路のインピーダンス特性に高いピークが発生する。この現象を「反共振」と呼ぶ。このピークは、2つのコンデンサのESRの差が大きいほど、高く急峻になる。つまり、低インピーダンスを実現できなくなってしまう。そこでESRをある程度の大きさに調整し、Q値を適度に低下させておけば、反共振のピークを低く抑えられるというわけだ。

この目的は、「電源分配回路の雑音を最小化することにある。そのためには、インピーダンス特性の底部がバスタブ曲線のように平坦になるように、急峻なピークを取り除いておくことが望ましい。単にある周波数帯域にわたるインピーダンスの平均値が低ければ良いというわけではない」(Sun Microsystems社のNovak氏)。

このようにQ値を低減することで反共振を抑える考え方自体は、決して新しいものではない†1)。しかし、この考え方に基づく対策部品が出始めたのはここ数年である。高度化する電源分配回路へのニーズに電子部品メーカーが応えた格好だ。国内では、セラミック・コンデンサを手掛けるTDKや村田製作所がユーザーごとに個別対応で出荷に応じるほか、太陽誘電も開発を検討中だという。導電性高分子コンデンサを得意とする三洋電機もすでにESR調整品を供給中だ。

ただし、「ESRの調整」が実際に意味するところは、コンデンサの種別によって若干異なる。セラミック・コンデンサに比べて原理的にESRの大きい導電性高分子コンデンサを手掛ける三洋電機は、「従来はESRの最大値しか保証していなかったが、2年ほど前からは、要望するユーザーに対しては最小値も保証するようにした」(三洋電機 電子デバイスカンパニー キャパシタ事業部 技術部 応用技術課の課長を務める石田秀樹氏)。つまり「ESRの調整」とは、ESRの値を一定範囲に収めることを意味する。

それに対してセラミック・コンデンサを手掛けるTDKは、従来品に比べてESRを高めに調整した品種を供給する(図4)。「これまでのセラミック・コンデンサは、静電容量の値に反比例してESRが小さくなるという品揃えだった。そこで、同じ静電容量でもESRの値が従来品よりも高い複数の品種を開発した」(TDK-MCCの技術企画部 技術企画課 で係長を務める富樫正明氏)。

図4 ESRを調整して反共振を抑える (a)はTDKが開発したESR調整セラミック・コンデンサ。電源側の内部電極とグラウンド側の内部電極は、それぞれ長辺に設けた外部電極で相互接続しておく。ここで短辺の外部電極に接続する内部電極(断面図中、赤色で示した内部電極)の数を変えれば、ESRを調整できる。具体的には、接続数が少ないほどESRは高くなる。(b)は、このコンデンサの効果を示した。いずれも10μFのセラミック・コンデンサだが、ESR調整品を使ってインピーダンス特性のピークを抑えた方が、雑音電圧の振幅が小さくなっている。出典:TDK

現時点でこうしたESR調整コンデンサが求められているのは、「特に高い電源品質を求めるハイエンド・コンピュータや通信インフラ装置に限られる。ただし今後は徐々に、ほかの用途にも広がるだろう。民生機器であっても、ESR調整コンデンサを使えば電源分配回路の設計が容易になる。メリットはあるはずだ」(Sun Microsystems社のNovak氏)。

また村田製作所によれば、DC-DCコンバータの小型化に取り組む設計者からは従来から、ESRを高めに調整したセラミック・コンデンサを求める要望が強かったという。「アルミ電解コンデンサやタンタル・コンデンサを、セラミック・コンデンサの大容量品で置き換えたいが、Q値が高く発振しやすいため使いにくいという声が上がっていた」(村田製作所 コンポーネント事業本部 企画管理部の部長を務める林幸広氏)。

1つの部品で「広く低く」

次に紹介するのは、単一の部品で広い周波数帯域にわたって低いインピーダンスを実現することを狙った、新型のコンデンサである。ボードに搭載するデカップリング・コンデンサの個数を大幅に削減しながら、電源系雑音を広い帯域にわたって抑制できるとする。

従来のコンデンサでは、周波数が高くなれば高くなるほど、ESLの影響が大きくなる。そこで高周波領域でのデカップリング効果を確保するために、数多くのコンデンサを並列に接続する手法が採られていた。その結果、例えばパソコンでは、「プロセッサ当たり30〜40個のセラミック・コンデンサが周辺に配置されている」(TDK-MCCの富樫氏)。「マザーボード全体では、コンデンサの搭載数は600〜1000個に達する」(アイキャストの代表取締役社長である遠矢弘和氏)。電源分配回路の実装面積やコストがかさむ。

広帯域/低インピーダンス特性を武器に複数のコンデンサの置き換えを狙う対策部品の代表格は、導電性高分子コンデンサを応用したNECトーキンの「プロードライザ」だ(図5)。1対のコンデンサ電極を伝送線路構造とした4端子部品である。「GHzの周波数まで低く平坦なインピーダンス特性」をうたう。例えば静電容量が200μFの品種は、部品単体のインピーダンスが100k〜1GHzにわたって10mΩ以下だとする。電源分配回路とデジタルLSIの間に挿入することで、LSIの高周波スイッチング電流による雑音の影響を抑えられる。

図5 線路型のデカップリング部品 NECトーキンのプロードライザである。デジタルLSIと電源分配回路の間に挿入して使う。1対のコンデンサ電極を伝送線路として機能させることで、広帯域にわたってインピーダンスを低く抑えた。出典:NECトーキン

2003年に市場投入を開始した。現在は、「Cellプロセッサを搭載するソニー・コンピュータエンタテインメントの家庭用ゲーム機『プレイステーション 3』への供給がほとんどだが、ノート・パソコン向けも増えてきた。さらに、徐々にではあるが、ハイエンドFPGAを搭載する通信インフラ機器などで採用が始まっている状況だ」(NECトーキンのマーケティング本部 ソリューション技術部で部長を務める堀仁孝氏)。

ただしプロードライザは、同社が目指す雑音対策部品の完成形にまだ達していないという。部品単体としてのインピーダンス特性は優れているが、使い方が難しいからだ。すなわち、ボードへの実装方法によっては、期待した雑音抑制効果が得られない。例えば、プロードライザとデジタルLSIの間をつなぐ電源プレーンとグラウンド・プレーンが共振する危険性がある。これを回避するためには、現時点ではかなりの設計ノウハウが必要だという。

そこで同社は、このプレーン共振を抑える対策部品を2008〜2009年をめどに開発する考えだ。「これをプロードライザに組み合わせれば、理想的な対策手法が完成する」(同氏)。表面実装型でありながら、基板埋め込み型コンデンサと同じような効果を生む部品だという。すなわち「ESLが極めて小さいコンデンサをデジタルLSI直下の電源/グラウンド・プレーンに接続したかのように、高い共振抑制効果が得られる」(同氏)とする。

実現方法の詳細は明らかにしていないが、表層の部品搭載用パッドと電源/グラウンド・プレーンを接続するビア・ホールのインダクタンス成分を、何らかの手法で電磁気的に無効化するようだ。

フィルタ効果高い損失線路

広帯域にわたって低いインピーダンスを備え、コンデンサの置き換えを狙う対策部品はほかにもある。アイキャストの「低インピーダンス損失線路(LILL:Low Impedance Lossy Line)」である。この部品は、同社の代表取締役社長である遠矢氏がNECの中央研究所に所属していた2000年に開発したものだ*4)。その後NECは事業化を断念したが、同氏がアイキャストで実用化に乗り出した。

導電性高分子コンデンサ材料を電極に使った伝送路構造を備える4端子部品である。プロードライザと同様に、電源分配回路とデジタルLSIの間に挿入して使う。ただし「プロードライザに比べて、さまざまな面で優れている」(同氏)と主張する。具体的には、広帯域/低インピーダンスの特性に加えて、高い挿入損失を備えており、雑音を減衰させる効果が高いという。このほか、外形寸法が幅1mm、長さ10〜30mm程度と比較的小さく、ボード上で雑音の影響が懸念されるさまざまな場所に搭載できることや、価格を20〜40円と安価に設定できることなどを挙げる。「2009年の早い時期に量産を始めたい」(同氏)とする。

「直列にインダクタ」を提案

数GHzと極めて広い周波数帯域にわたって、デジタルLSIの電源に重畳した高周波雑音を阻止できると主張するのは、ケイアールエフエムだ。巻線型コイルの両端にショートリング(防磁枠)を取り付けた独自の構造でQ値を抑え、広帯域にわたって高い減衰量を確保した2端子フィルタ素子「コイフィル」と、このコイフィルとコンデンサを組み合わせたT型/π型の3端子フィルタ素子「パワフィルタ」を提案する。

いずれも、デジタルLSIに接続する電源パターンに直列に挿入して使う。インダクタを挿入することで、デジタルLSIで発生した高周波雑音が電源分配回路に流入しないように阻止する役割を果たす。「コンデンサでは、広い帯域にわたって高周波雑音を阻止することは不可能である。そこでインダクタに目を付けた」(同社の代表取締役を務める小宮邦文氏)。

雑音に対する減衰量の周波数特性は、3端子貫通コンデンサに近い。ただし、「3端子コンデンサは、グラウンド端子の配線が長いと特性が劣化し、減衰量を確保できる周波数の上限が大きく低下してしまう。これに対してパワフィルタは、特性劣化が小さいという特徴がある」(同氏)と説明する。

すでに医療機器や計測機器など性能を最優先する用途で採用事例があるとするが、「これら以外ではあまり普及していない。理由は明らかだ。単価が約300円と高いからである。2008年中にこの技術のライセンス供与を始める予定で、仮に大手電子部品メーカーが大量生産に乗り出せば、5円程度に引き下げられるだろう」(同氏)という。このほか、外形寸法がパワフィルタの表面実装品で4.0mm×5.5mm×1.8mmと比較的大きいという課題もある。「小型化は難しい。ただ、グラウンドへの配線長が特性に影響しにくいことから、ボード上の配置などに関する柔軟性は高い」(同氏)。

埋め込みコンデンサ実用に

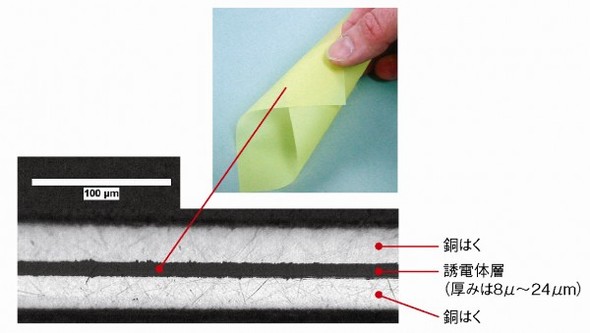

基板に埋め込むタイプのコンデンサも実用化が進んでいる。例えば、米Oak-Mitsui Technologies社の基板内蔵型コンデンサ材料「FaradFlex」である。「表面実装型のコンデンサに比べて、大幅に低いインピーダンスを実現できる」(FaradFlexなどEMC関連製品の技術営業を手掛ける米TechDream社の創設者でプレジデントを務める府川住広氏)ことが特徴だ。2004年に量産を始めており、すでにハイエンドのサーバー機器やルーター、半導体テスターなどに採用実績があるという。

銅箔(はく)をコア材とし、ごく薄いフィルム状の誘電体材料を挟み込んだ構造を採る。ユーザーは既存のボードの電源/グラウンド・プレーンをこれに置き換えればよい(図6)。誘電体層の厚みは、材料の品種によって異なるが8μ〜24μmと薄い。このため、「電源-グラウンド間の距離を極めて短くできることに加えて、デジタルLSIに最短距離で接続できる。この結果、広帯域/低インピーダンスを実現できる」(同氏)。

図6 基板埋め込み型コンデンサが実用に 電源/グラウンド・プレーンの間に高誘電率の絶縁体を挟み込む。例えば、誘電体層の厚みが12μmで比誘電率(1kHz)が10の品種では、埋め込みコンデンサ自体のインピーダンスは数M〜1GHzにわたって0.1Ω以下とする。出典:米Oak-Mitsui Technologies社

コストについては、「ケース・バイ・ケース。材料自体のコストはFR-4の約2倍と高いが、プリント配線基板の層数が多ければ、コスト増加率は低い。例えば20層基板であれば、材料コストの増加は5〜15%程度にとどまる。さらに、これを採用することでデカップリング・コンデンサを取り去ることができれば、結果としてボード全体のコストを低減できる可能性もある」(同氏)と説明する。

ツールの助けは不可欠

ただし、これらの新型部品を採用したとしても、必ずしも電源品質を確保できるわけではない。対策部品はそれ自体の特性だけでなく、その使い方が極めて重要だからだ。ボードのどの位置に、どうやって実装するかによって、得られる効果はまったく変わってしまう。ボードの電源分配回路全体の特性を最適化するように配置しなければ意味がない。

ところがこの最適化作業は、実際にはそれほど簡単ではない。作業の進行が最適設計に向かっているかどうかを判断するためには、「デジタルLSIに供給される電源電圧は誤差範囲を超えていないか」、「プレーン共振によって空間に放射されるEMIの大きさは許容範囲内か」、「伝送信号のアイ・パターンに悪影響を与えていないか」といった評価が必要になる。こうした特性をボード設計者が手計算で求めることは非現実的である。かといって、試作機をEMCサイトに持ち込んで、測定と対策部品の追加や削除を繰り返す旧来の手法は、効率的とはいえない。

対策部品の効果をうまく引き出し、ボードの最適設計を実現するためには、コンピュータ・ツールの活用が不可欠である。実際に、対策部品メーカーでありEDAツール・ユーザーでもあるパナソニック エレクトロニックデバイスは、「対策部品は使い方次第だ。そこで当社は、機器メーカーが開発する特定のボードに対して、電源系雑音を軽減する観点から、部品の最適配置や基板レイアウト設計までも提案する取り組みを進めている。これには電磁界解析ツールや回路シミュレータなどのツールが不可欠である。今後は、こうしたツール上での検証が主流になるだろう」(同社の西山氏)と指摘する。

こうした背景からここ最近、EDAツール・ベンダー各社は「パワー・インテグリティ向け」をうたうツールの投入を加速させている。以下に、こうしたツールの使いどころや新機能を解説しよう。

プレーン共振解析が普及

ボードのパワー・インテグリティに向けてすでに広く解析されているのは、電源プレーンとグラウンド・プレーンの間の共振である。プリント配線基板の設計データを基に、プレーン共振による電位変動の大きさを解析し、色分けして表示する。米Ansoft社やNEC情報システムズ、米Sigrity社などが供給するEDAツールにこの機能が搭載されている。

ただし各社のツールは、解析プログラムが採用するアルゴリズムや、解析結果の精度や活用方法などに違いがある。例えばAnsoft社のツールとNEC情報システムズのツールでは、採用するアルゴリズムが異なる。

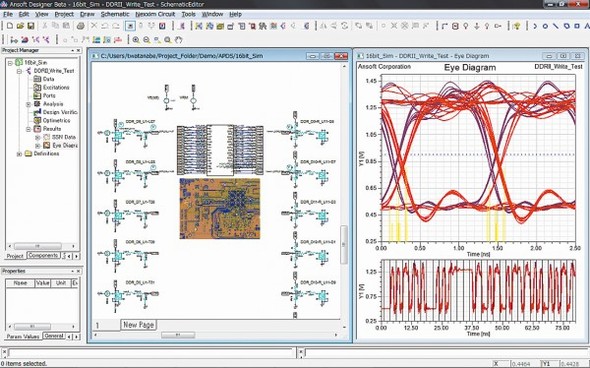

Ansoft社は、ボードやICパッケージのパワー・インテグリティに向けた2次元電磁界解析ツール「SIwave」を供給する。使用している解析アルゴリズムは有限要素法である。プレーン共振解析のほか、電源分配回路のインピーダンス特性を抽出する機能や、入出力回路の同時スイッチング雑音に起因したEMIを解析する機能も備えた(図7)。「適応型のメッシュ生成技術を採用しており、ボード全体など規模の大きい対象物を高い精度で解析できることが特徴だ」(アンソフト・ジャパンの渡辺氏)。価格は700万円で、プリント配線基板向けCADツールとのインタフェースもオプションで提供する。

図7 電源系雑音の影響をアイ・パターンで評価 DDR2対応メモリーを搭載したプリント配線基板のインピーダンス特性を2次元電磁界解析ツール「SIwave」で抽出し、それをモデルとして回路シミュレータ「NEXXIM」でデータ信号のアイ・パターンに対する同時スイッチング雑音の影響を解析した。出典:アンソフト・ジャパン

一方のNEC情報システムズは、EMC設計ルール・チェック・ツールである「DEMITASNX」に、プレーン共振を簡易的に解析する機能を搭載している。解析アルゴリズムとしてPEEC(Partial Element Equivalent Circuit)法を採用しており、電源/グラウンドの形状と両プレーンに接続したコンデンサを、ともに集中定数素子の等価回路モデルとして扱う。「このツール本来の機能は、プリント配線基板の設計データをあらかじめ用意した設計ルールに照らし合わせ、EMIを増大させる危険性が高いレイアウトを見つけ出すことだ。従って、プレーン共振の解析精度は、対策効果を手早く確認できればよい程度と割り切っている。電磁界解析ツールに比べれば精度は低いが、プリント配線基板の設計には十分だ」(同社のITソリューション事業部 設計ソリューショングループでグループマネージャーを務める恵谷誠至氏)という。価格は400万円である。

電源品質に焦点絞る

さらにNEC情報システムズは、パワー・インテグリティ向けツールの強化に乗り出した。第1弾は2007年6月に市場投入したDEMITASNXの改良版「ver.3.8」で、プレーン共振の解析結果を基に、電源/グラウンドの電位変動を抑えるようにデカップリング・コンデンサを自動的に追加する機能を用意した。追加するコンデンサの最大個数と電位変動の許容上限値を指定すると、追加すべきコンデンサの配置を提示する。

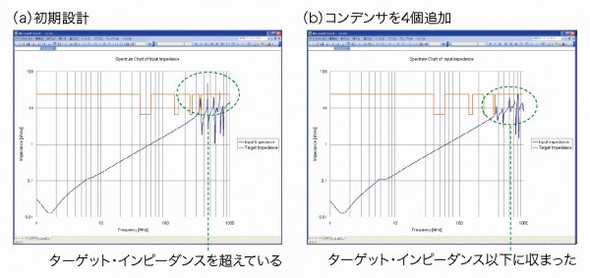

第2弾は、電源分配回路のインピーダンス特性を解析する新ツール「PI Stream」だ。DEMITASNXのプレーン共振解析アルゴリズムを流用して新たに開発した。「DEMITASNXはEMI対策向けツールであり、プレーン共振解析の狙いはEMI抑制にあった。これに対してPIStreamは、パワー・インテグリティに焦点を絞った」(ITソリューション事業部 設計ソリューショングループのマネージャーを務める矢口貴宏氏)。ベータ版を2007年12月中旬までに用意し、製品版を同12月末ころに発売する予定である。価格は250万円程度に設定する考えだ。

使い方はこうだ。ユーザーはプリント配線基板の設計データを読み込んで、電源分配回路のインピーダンスを観測する地点を指定する。実際には、雑音源になり得るLSIの搭載位置の中心点を指定すればよい。解析を実行すると、観測点における電源分配回路のインピーダンス特性が表示される仕組みだ(図8)。

図8 インピーダンス特性を素早く解析 「PIStream」の実行画面の例である。(a)は初期のボード設計における電源分配回路のインピーダンス特性。高周波領域でターゲット・インピーダンスを超えてしまっている。(b)は、(a)にデカップリング・コンデンサを4個追加した結果である。ターゲット・インピーダンス以下に抑えられた。これらの解析に要する時間は数十秒と短い。出典:NEC情報システムズ

解析結果とともにターゲット・インピーダンスを表示する機能を用意した。デカップリング・コンデンサを追加/削除したり、電源/グラウンドのレイアウト形状を変更したりしながら解析を繰り返し、ターゲット・インピーダンス以下にインピーダンスを抑えられる最適設計を探るといった使い方が可能である。「将来的には、ツールが自動的に最適設計を見つけ出す機能を用意したい」(同氏)。

ターゲット・インピーダンスは、LSIの電源電圧とその許容誤差、消費電流、周波数の情報を与えることでツールが自動的に算出する。このほか、周波数ごとのインピーダンスの値をテーブル形式のファイルで与えることも可能だ。

さらに同社は今後、LSIのターゲット・インピーダンスの情報をあらかじめ半導体ベンダーから入手し、ライブラリ化してツールに組み込むことを目指す。しかし現時点では一般に、半導体ベンダーはターゲット・インピーダンスを公開していない。「ターゲット・インピーダンスには、半導体ベンダーが秘匿すべき情報は含まれないはずだ。従って、IBIS(I/O Buffer Information Specification)モデルを提供するのと同様に、ターゲット・インピーダンスのモデルを提供することは不可能ではないだろう」(同氏)。すでに、ある半導体ベンダーと話し合いを始めているという。

フルウエーブ3次元で解く

このほか、Maxwellの方程式を簡略化せずに解くいわゆるフルウエーブの3次元電磁界解析ツールも、将来はパワー・インテグリティを考慮したボード設計フローに適用が進みそうだ。このツールは高い精度が得られる半面、大規模な構造物を解析するには、高い処理性能や大容量メモリーなど大きなコンピュータ・リソースが必要なことや、解析結果の妥当性の判断に専門的な知識が求められることから、現在は主に学術的/工業的な研究に利用が限られている。ボードの設計フローに組み込むことは現実的ではない。

だが今後、3次元電磁界解析ツールの処理速度が向上するのは間違いない。独Computer Simulation Technology(CST)社の3次元電磁界解析ツール「MICROWAVE STUDIO」の国内販売とサポートを手掛けるエーイーティーによれば、「ハードウェア・アクセラレータや並列計算など、高速化の手段は多い。個人的な意見だが、これから5年、あるいは10年といった期間で、パワー・インテグリティに関する試行錯誤のほとんどが3次元電磁界解析ツール上で実行できるようになるのではないか。そうなれば、試作機すら不要になるかもしれない」(同社 技術部の上田千寿氏)。

現時点でも、「簡略化したモデルを使えば、物理的なパラメータを変更しながら解析を繰り返すことで、パワー・インテグリティに関する定性的な知見を蓄積する用途に使える」(同氏)という。この情報は例えば、パワー・インテグリティを考慮した設計ルールを確立する際に活用可能だ。

【参考文献】

†1)伊藤健一、「ノイズと不要輻射のはなし」、日刊工業新聞社、1998年7月発行

【注釈】

*1)数GHzの内部クロック周波数がそのままボード上に電源系雑音として現れるわけではない。内部クロック周波数は、ボード上で供給する外部クロック信号を基に、チップに集積したPLL(Phase Locked Loop)回路で生成しているからだ。チップ上の静電容量やインダクタンスがフィルタとして機能するため、このクロック信号はボード上には流出しにくい。ただし、ボード上を伝わる外部クロック周波数もすでに数百MHzに達しており、その高調波成分は容易にGHzのオーダーに達する。

*2)di/dtによる交流的な雑音のほか、直流電圧降下(いわゆるIRドロップ)も電源電圧の誤差になる。このため電源電圧がデジタルLSIの誤差範囲に収まるかどうかを詳細に検討するためには、IRドロップ解析も欠かせない。

*3)2007年1月29日〜2月1日に米国で開催された電子機器設計技術の学会「Design Con 2007」では、米Sun Microsystems社のIstvan Novak氏を中心に、ESR調整コンデンサに関する技術フォーラムやパネル・セッションが開催され、参加者の関心を集めていた。

*4)発表当時は、「低インピーダンス線路素子(LILC:Low Impedance Line Structure Component)」と呼んでいた。

Copyright © ITmedia, Inc. All Rights Reserved.