CMOSが拓く次の応用 〜 ISSCC 2009開催:アナログ設計(4/5 ページ)

半導体集積回路の最新技術が世界中から集結する国際学会「ISSCC(IEEE International Solid-State Circuits Conference)」。2009年2月8〜12日に米カリフォルニア州サンフランシスコで開催された「ISSCC 2009」から、半導体集積回路の新たな応用分野を拓く取り組みを紹介する。

第3部 3次元実装で制約を解き放つ、低電力化と小型化の切り札に

メモリーやマイクロプロセッサなど、複数枚の半導体チップを縦方向に積層して1つのパッケージに収める「3次元実装技術」が注目を集めている。SiP(System in Package)型モジュールに適用すれば、プリント基板の実装面積を大幅に削減できるからだ。ただし、3次元実装技術は、チップ間インターフェースの入出力帯域幅を広げにくいという課題を抱えている。これまで3次元実装では一般に、ワイヤー・ボンディングによってチップ間を接続していた。電極間の配線長が数mmと長いため、インダクタンス成分による伝送信号の品質劣化が大きく、通信速度を高めにくい。その上、インターフェース回路の消費電力も大きくなってしまう。

これに半導体プロセス技術の微細化が追い打ちをかける。微細化によってマイクロプロセッサなどの処理性能が向上すれば、チップ間インターフェースには一段と広い入出力帯域幅が求められる。ところが、チップに集積した論理回路の処理性能が微細化によって向上する割合に対して、インターフェース回路の入出力帯域幅は向上の割合が低い。「論理回路はチップの全面に集積できるのに対し、ワイヤー・ボンディングを使う場合は、インターフェース回路の入出力電極をチップの周辺にしか配置できない」(慶応義塾大学理工学部電子工学科の教授である黒田忠広氏)からだ。微細化が進めば進むほど、両者の差は広がってしまう。「これまではインターフェース回路に新規技術を導入することなどで、なんとか論理回路との性能差の拡大を抑えてきた。しかし、2000年ころから、通信速度と消費電力の壁が見えてきた」(同氏)。

そこで次世代の3次元実装技術として、積層した複数のチップを貫くビア・ホールによって互いを有線接続する「シリコン貫通電極(TSV:Through Silicon Via)」のほか、誘導結合や容量結合を利用した各種の無線方式が名乗りを上げている。ただしTSVについて黒田氏は、「コストが課題である。同技術の推進団体が掲げる目標投資額からざっと試算すると、2008年の時点でDRAMチップ1枚当たり25円程度のコスト増になる。これは、現実的には受け入れられないだろう」と指摘する。それに対し同氏が提唱する誘導結合方式については、「TSVと同等の性能が得られる上、製造プロセスは標準的なCMOS技術を適用できるため、コストについてはワイヤー・ボンディング並みだ」と主張している。

CPUとSRAMを誘導結合で3次元実装

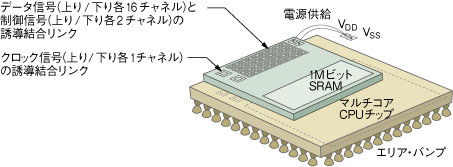

慶応義塾大学と日立製作所、ルネサス テクノロジの3者は共同で、CPUチップとSRAMチップを3次元積層して両チップを誘導結合方式で無線接続し、システム・レベルの動作を検証した成果について発表した(図1)(講演番号は28.7)。今回利用した誘導結合に基づく3次元実装技術は、慶応義塾大学の黒田氏が以前から提唱していたものだ。同氏はこの技術を「ワイヤレスTSV」と呼ぶ。

図1 検証した3次元実装システム CPUを下側、SRAMを上側にして両チップの裏面同士をはり合わせ、CPUの表面側に設けたエリア・バンプで支持基板に接続した。CPUは8個のコアを集積したマルチコア品。90nm技術で製造し、大きさは10.61mm×9.88mm。SRAMは65nm技術で製造した1Mバイト品。大きさは6.2mm×6.2mm。電源については、CPUは表面のエリア・バンプ経由で、SRAMは表面に設けた電極にワイヤー・ボンディングを介して、それぞれ供給した。出典:慶応義塾大学理工学部電子工学科の教授である黒田忠広氏の説明資料

3者は今回の成果について、「誘導結合に基づく3次元実装技術の有用性を実証できた」と説明する。具体的には、ルネサス テクノロジが製品として供給しているCPUとSRAMを基に誘導結合のインターフェース回路を作り込んだチップを使って、実際のSiP製品に近い条件において、チップ間のデータ通信を高い信頼性で確立できることを確かめた。SRAMの全ビットにCPUからアクセスし、読み書きできることを確認したという。

両チップの表面側にはあらかじめ誘導結合用のコイルを、両チップをはり合わせた際に対向する位置に作り込んだ。これらが、上り方向(CPUからSRAM)と下り方向(SRAMからCPU)それぞれ16チャネルのデータ通信路として機能する。チャネル当たりのデータ伝送速度は600Mビット/秒である。従って、両チップ間の入出力帯域幅は、600Mビット/秒×16チャネル×2より、合計で19.2Gビット/秒に達する。

今回の検証でワイヤレスTSVの実現に向けてCPUとSRAMに追加した回路の面積は2.88mm2で、1.92Gビット/秒伝送時の消費電力は19.2mWだった。従って、1Gビット/秒当たりの回路面積は0.15mm2で、1ビット当たりの消費電力は1pJになる。すなわち、基板上に2枚のチップを並べて実装してDDR2インターフェースで両者を有線接続する場合に比べて、送受信回路部分の面積については1/3、消費電力については1/30になったとしている。

電源の工夫でSSDを低電力/小型化

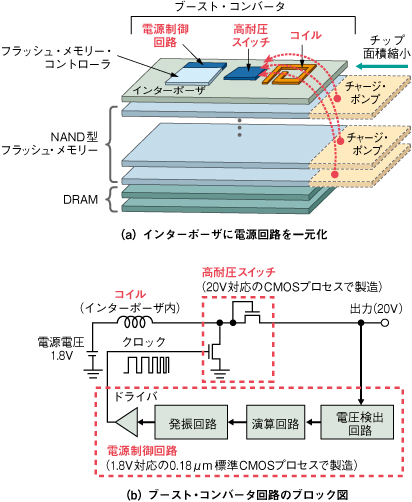

東京大学は、複数枚のNAND型フラッシュ・メモリー・チップを積層する1パッケージ型のSSD(3次元SSD)に向けた電源システムについて発表した(講演番号は13.2)。これまでNAND型フラッシュ・メモリーのチップごとに必要だった電源回路を1つにまとめたことに加えて、電源回路そのものに工夫を施した(図2)。この電源システムを採用すれば、大幅な低消費電力化と小型化が図れるという。具体的には、電源システムと1つのNAND型フラッシュ・メモリー・チップを組み合わせた場合で比較しても、従来に比べて消費電力を68%低減できる。また、NAND型フラッシュ・メモリーの面積をチップ当たり5〜10%削減可能だとする(40nmプロセス技術で製造した場合)。「SSDはフラッシュ・メモリーを多数利用するので、低消費電力化と小型化の効果はさらに顕著になる」(東京大学大学院工学系研究科の電気系工学専攻で准教授を務める竹内健氏)。

図2 NAND型フラッシュ・メモリーの昇圧回路を一元化 開発した電源回路を適用する3次元SSDの構成(a)と、電源回路のブロック図(b)である。これまではフラッシュ・メモリー・チップそれぞれに集積していた電源回路を、一元化してインターポーザ(基板)に搭載した。電源回路そのものも新たな仕組みを採用しており、クロック信号を制御する仕組みや、狙った出力電圧まで昇圧する際のアルゴリズム、これらを実現する回路技術に独自性があるという。出典:東京大学竹内研究室

現在開発が進められている3次元SSDは、低消費電力化と小型化の観点から課題があった。詳しくはこうだ。フラッシュ・メモリーのセルにデータを書き込むには、20Vと高い電圧が必要である。通常、この電圧はフラッシュ・メモリー・チップに供給される1.8Vや3.3Vといった電源電圧をチップ内部の電源回路で昇圧して作り出す。この電源回路の消費電力はメモリー・チップ全体の35%程度(電源電圧が3.3Vのとき)、チップ専有面積に関しては5〜10%を占める(40nmプロセスで製造した場合)。しかも、SSDの大容量化を図ろうとフラッシュ・メモリー・チップの積層数を増やせば増やすほど、SSD全体で見ると電源回路の面積と消費電力が増えてしまう。

東京大学が提案した手法はこのような課題を解決するため、電源回路を共通化してインターポーザ(基板)上に実装するものだ。開発した電源回路は、コイルと高耐圧スイッチ(FET)、電源制御回路で構成したもので、特殊な製造プロセスは不要だ。高耐圧スイッチと電源制御回路の製造には、古い世代のCMOSプロセス技術が使える。コイルについては、インターポーザの配線を活用できる。従って、「電源回路を共通化することによる製造コストの増加は、ほとんどない」(東京大学生産技術研究所で教授を務める桜井貴康氏)という。

さらに、電源回路として独自のブースト・コンバータ回路を採用したことも、課題の解決に寄与した。これまでは一般に、コンデンサを20段ほど並べたチャージ・ポンプ回路が使われてきた。東京大学が採用したブースト・コンバータの回路構成そのものは、前述のようにコイルと高耐圧スイッチ、電源制御回路からなり、取り立てて目新しいものではない。ただし、「高耐圧スイッチを駆動するクロック信号を制御する仕組みや、狙った出力電圧にまで昇圧する際のアルゴリズム、これらを実現する回路技術に独自性がある」(東京大学の竹内氏)という。

Copyright © ITmedia, Inc. All Rights Reserved.