強誘電体SRAMやスピンMOS FETが開発、新材料や新機構で微細化限界打ち破る(前編):プロセス技術(2/2 ページ)

Si(シリコン)以外の新たな材料や、新たな動作機構を採用することで、先が見えつつある微細化の限界を引き延ばそう、または乗り越えていこうという研究開発が進められている。

しきい値電圧がSRAMの安定度高めるように動的変化

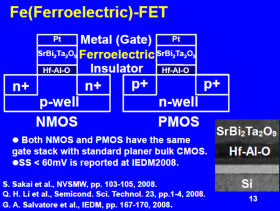

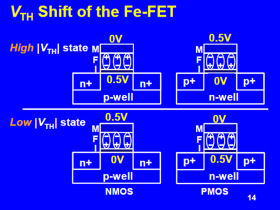

強誘電体をゲート電極に使うことで得られる最大の利点は、データの書き込みや読み出し、スタンバイといったSRAMの各動作が安定するように、MOS FETのしきい値電圧Vthが自動的に変わる点である。ゲート電極に印加する電圧が「High」または「Low」という状態に応じて強誘電体の分極状態が変わり、結果、しきい値Vthが0.1V程度変わる(図3)。

図左(図3)は強誘電体SRAMの構造。Si基板にHfAlO膜とSrBi2Ta2O9膜を積層した。強誘電体材料は、産業技術総合研究所エレクトロニクス研究部門フロンティアデバイスグループが開発したもの。図右(図4)は、しきい値電圧Vthが変わる仕組み。上部は、しきい値が高くなる場合における、強誘電体膜の分極の様子。下部は、しきい値が低くなる場合における強誘電体膜の分極の様子である。ゲート電圧に応じて分極の方向が変わることで、チャネルの電子数が変わり、しきい値電圧Vthが変化する。

図左(図3)は強誘電体SRAMの構造。Si基板にHfAlO膜とSrBi2Ta2O9膜を積層した。強誘電体材料は、産業技術総合研究所エレクトロニクス研究部門フロンティアデバイスグループが開発したもの。図右(図4)は、しきい値電圧Vthが変わる仕組み。上部は、しきい値が高くなる場合における、強誘電体膜の分極の様子。下部は、しきい値が低くなる場合における強誘電体膜の分極の様子である。ゲート電圧に応じて分極の方向が変わることで、チャネルの電子数が変わり、しきい値電圧Vthが変化する。仮に、n型MOS FETの場合にゲート電極が0.5V(High)のとき、p型ウエハーのグラウンド電圧が0V(Low)だとする。このとき、強誘電体中では、ゲート電極側に負電荷が帯電するように、一方のチャネル側には正電荷が帯電するように分極する。結果、チャネル中には負電荷が引き寄せられ、しきい値電圧Vthが下がるという仕組みである(図4)。

これまで、基板にバイアス電圧を印加することで、基板上のMOS FET全体のしきい値電圧を変える試みはあった*3)。ただ今回のように、MOS FETのそれぞれのしきい値が変わるデバイスは、従来のSi材料のみを使ったMOS FETでは現実的ではない。強誘電体という新材料を使ったからこそ、なしえたことなのである。

Vwindowが30mVから137mVへ

以上のように、しきい値電圧Vthが変わる効果は顕著である。例えば、p型MOS FETがオンするときにはVthが下がってオンしやすいようになり、n型MOS FETがオフするときにはVthが上がってオフしやすいようになるからだ。「単純な構造だけれど、SRAMの動作が安定するように、すべてのつじつまが合っている」(竹内氏)。

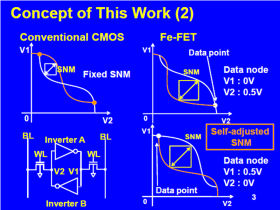

この結果、SRAMの動作安定性を示す静的雑音余裕(SNM:Static Noise Margin)や、しきい値電圧のばらつきの許容値(Vwindow)を大きく高められる。これは、電源電圧を今よりも引き下げた場合でも、安定して動作させられることを意味する(図5)。

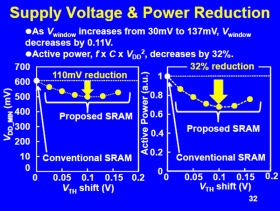

竹内氏の研究グループでは、計算機シミュレーションと実際に試作した強誘電体SRAMセルを使って、強誘電体SRAMの動作を解析した。しきい値電圧Vthの変化幅が0.1Vで、電源電圧が0.5Vの条件のとき、Vwindowは30mVから137mVに広がった。これは、電源電圧をおよそ0.11V下げられることを意味し、これに伴って動作時消費電力を32%削減可能だとする(図6)。

図左(図5)は、従来のSRAMとの違い。図中の上図左側が従来のSRAMの静的雑音余裕(SNM)、右側が強誘電体SRAMのSNMの様子である。SNMが広がるように、しきい値電圧が変化する。図右(図6)は、強誘電体SRAMの効果。SRAMを安定に動作させつつ、電源電圧を0.11V引き下げられる。これによって、動作時消費電力を32%削減可能だとする。

図左(図5)は、従来のSRAMとの違い。図中の上図左側が従来のSRAMの静的雑音余裕(SNM)、右側が強誘電体SRAMのSNMの様子である。SNMが広がるように、しきい値電圧が変化する。図右(図6)は、強誘電体SRAMの効果。SRAMを安定に動作させつつ、電源電圧を0.11V引き下げられる。これによって、動作時消費電力を32%削減可能だとする。「現在、材料はそのままに製造プロセスを改善することで、Vwindowを100mVから110mVへ広げることに各メーカーがしのぎを削っている。ゲートの材料を変えるだけで、Vwindowが劇的に変わる意義は大きい。電源電圧が現状の1.2Vの場合は、今回の技術のインパクトは薄いかもしれないが、電源電圧を0.4Vや0.5Vにまで下げる必要に迫られたとき、生きてくる」(竹内氏)。例えば、電源電圧が0.5VのときのSNMは、0.12Vから0.19Vに広がる。

さらに、リーク電流の抑制や動作速度の高速化にも効果があるとする。試作したSRAMセルで実測したところ、しきい値電圧を0.1V幅で変えることで、リーク電流を42%削減可能であることを確認した。

Copyright © ITmedia, Inc. All Rights Reserved.