微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(2/10 ページ)

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000 年代に入り、状況が変わってきた。

第1部 幾何学的スケーリングを超えた先

より速く、より小さく、より安く……。1950年代に産声を上げたトランジスタの集積回路技術は、わずか50年あまりの間に急速に発展した(図1)。

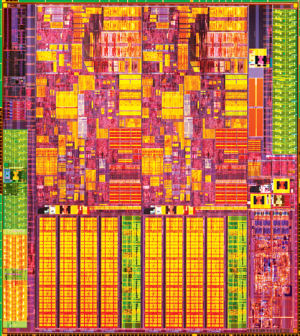

米Intel社が1971年に業界で初めて製品化したプロセッサ「Intel 4004」は、わずか2300個のトランジスタしか集積しておらず、動作周波数は500kHz 〜 741kHzだった。そして37年後の2008年に同社が製品化したプロセッサ「Core i7」のトランジスタ数はおよそ7億3000万個に達し、動作周波数は最大3.6GHzに向上した。

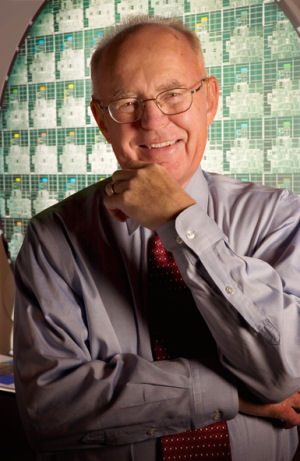

このような半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることに疑問の余地はないだろう。1つ1つのトランジスタの寸法が小さくなれば、半導体チップの面積を大きくすることなく、載せられるトランジスタの数は増える。50年近くの間、同一面積の半導体チップに集積できるトランジスタ数は約2年ごとに倍増し続けてきた。これが、米Intel社の Gordon E.Moore氏(図2)がシンプルな経験則として1965年に提案した「ムーアの法則(Moore’s Law)」である。

さらなる微細化に向けた研究開発は、現在も活発に続いている。例えば、Intel社は2010年1月に32nm世代*1)の製造技術を採用したプロセッサ・コア(開発コード「Westmere」)を発表した。これに続く、22nm世代の品種の開発も進めている。米Qualcomm社は、台湾TSMC(TaiwanSemiconductor Manufacturing Company) 社と協業し、28nm世代の製造技術の開発に取り組むことを発表した。

これまで、微細化は順調に進んできたように見える。ところが、50年近く続いてきた微細化の流れが、2000年代に入って変わってきた。微細化を続けてきた結果、トランジスタの物性に起因するさまざまな問題が顕在化してきたのである。

今後さらに微細化を推し進めるとするなら、とても高いハードルをいくつも越えていかなければならない。現時点で、1Xnm世代とその先ははっきり見通すことは難しい。そこで、現在は微細化をさらに推し進めるために、Siトランジスタに新材料を融合する研究が進んでいる。新材料を導入することで、微細化のハードルを引き下げたり、新たな機能を付加するなどの取り組みだ。

万能薬だった微細化

トランジスタを微細化するメリットは大きかった。現在のICやLSIを構成する主要な要素は、MOS型電界効果トランジスタ(Metal Oxide Semiconductor Field Effect Transistor:MOS FET)である。このMOSFETを微細化すれば、消費電力の削減と、応答速度の向上、単位面積当たりの素子数の増加を同時に実現できる。これによって、LSI全体の消費電力は減り、処理性能は向上する。

一般に、処理性能を高めると消費電力は増大するが、微細化を進めれば消費電力を引き下げつつ、処理性能を高められる。さらに、微細化が進むと同様の機能を持つチップを、より小さく作れるようになる。

パソコンや携帯電話機、デジタル家電といった身の回りにある電子機器は、半導体の微細化の恩恵を受け、発展してきた。パソコンの処理性能は劇的に向上し、携帯電話機にはさまざまな機能が搭載されるようになった。電子機器の発展を、半導体の微細化が下支えしてきたのである。

微細化を進めるときには基本的に、「比例縮小の法則(スケーリング則)」を守らなければならない。微細化してもMOS FETの内部の電界を一定に保たなければならないという法則である。これを実現するには、ゲート部の長さや幅、ゲート部の絶縁体膜の厚さといった素子の各部を縮小すると同時に、Si基板の不純物濃度を高め、駆動電圧を引き下げる。その結果、MOS FETの素子面積が小さくなることはもちろん、ゲート部の静電容量が減り、動作が高速になる。さらに、駆動電圧や駆動電流も小さくなるため、消費電力量が減る。

Copyright © ITmedia, Inc. All Rights Reserved.