第13回 アナログ回路に不可欠な差動対:Analog ABC(アナログ技術基礎講座)(2/2 ページ)

今回からは新たに、「差動対」と呼ぶ基本回路の特長と動作の仕組みを説明します。差動対がなければ、現在のように電子回路が発展していないと言ってよいほど、重要な回路です。

同相雑音除去が最大の特長

差動対の最大の特長は、2つの入力信号の差分に対して動作する点です。言い方を変えると、差分に対してのみ動作し、位相が同じである(同相の)信号を打ち消します。

この点は、非常に重要です。この特長によって、電源や外部から信号に混入した雑音を除去できるからです。一般に2本の信号線を使う場合、外部から混入する雑音は各信号線に同相信号として重畳します。また前述のように、増幅器として機能するので、雑音が混入した小さい信号を「ひろう」には最適です。同相信号を除去する性能の指標は、「同相除去比(CMRR)」と呼び、オペアンプのデータシートなどに記載されています。

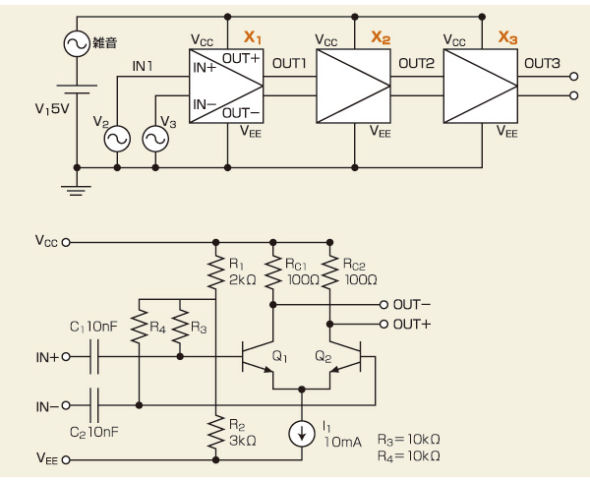

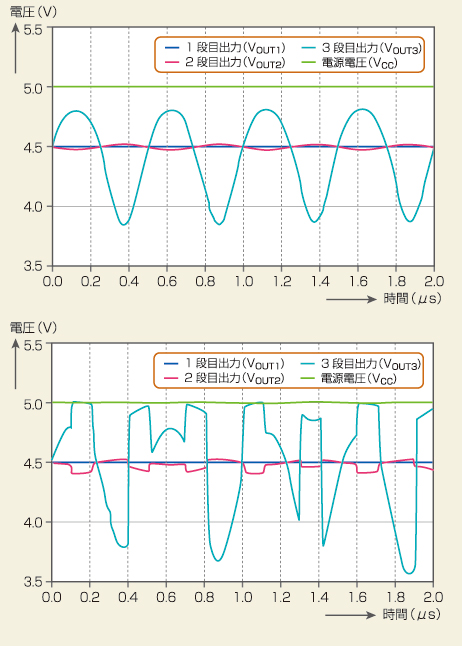

百聞は一見にしかず。2つの入力信号の差分に対して動作するという特長を、もう少し具体的な例で説明しましょう。図3は、通常のエミッタ接地増幅回路を3段直列接続して、0.1mVppの入力信号を増幅した例です。1段目と2段目、3段目のそれぞれの出力信号を示しました。図3(a)は電源電圧に雑音が重畳していない場合、図3(b)は電源電圧に5mVppの雑音が重畳した場合です。図3からは、電源電圧に雑音が重畳すると、出力信号は雑音の影響を大きく受け、ひずんでしまうことが分かります。

図3 電源電圧に雑音が含まれた場合のエミッタ接地増幅回路の出力 (a)は電源電圧に雑音が含まれていない場合の出力信号。(b)は5mVppの雑音が電源電圧に重畳した場合の出力です。3段接続したエミッタ増幅回路を使い、1段目の出力を青、2段目を赤、3段目を水色で示しました。

入力信号は0.1mVppに設定しましたので、5mVppと大きい雑音が電源電圧に載ってしまっては仕方がないとあきらめて、電源回路を改善するしかありません。

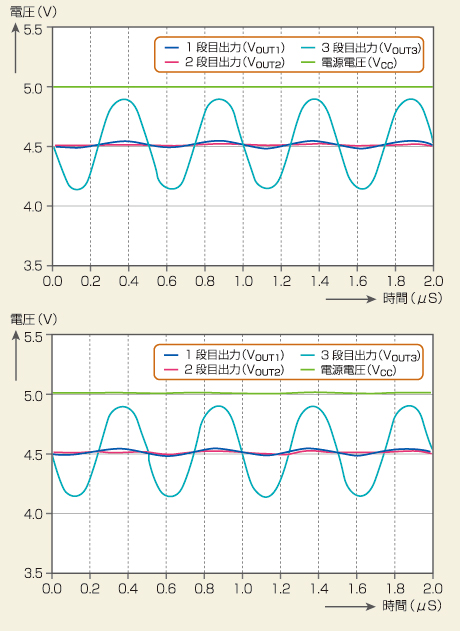

これに対して、図4に示した差動対を使った場合の出力結果が図5になります。入力信号が0.1mVppで、電源雑音が5mVppという条件はエミッタ接地増幅回路を使った場合と同じにもかかわらず、違いは一目瞭然(りょうぜん)です。図5(b)の出力信号に雑音の影響がほとんど出ていません。この圧倒的な差が、差動対の力です。このため、差動対はオペアンプやコンパレータだけではなく、LVDSやPCI Express、シリアルATAといった高速シリアル通信に必ず使われます。

差動対には、次のような特長もあります。2つの入力信号の端子のうち、片方を直流入力にすれば、この直流入力を基準として、交流信号を増幅する振幅レベルを調整できます。片方を直流入力にしたままで、利得を非常に高くしたり、正帰還を掛けたりすれば、コンパレータとしても使えます。

図5 電源電圧に雑音が含まれた場合の差動対の出力 (a)は電源電圧に雑音が含まれていない場合の出力信号。(b)は5mVppの雑音が電源電圧に重畳した場合の出力です。1段目の出力を青、2段目を赤、3段目を水色で示しました。

また、差動対の電流源の出力を変えられるように工夫すれば、利得も調整できます。電流源の出力電流を変える制御信号を入力信号にするならば、乗算器として使えます。

次回は、差動対の動作の仕組みを、数式を使いながら説明しましょう。

Copyright © ITmedia, Inc. All Rights Reserved.