先端FPGA用POL電源設計の勘所、DC-DCモジュールの活用法を紹介(後編):電源設計 DC-DCコンバーター(2/4 ページ)

1つの事例を紹介しよう。あるシステム設計者の電源に対する要求は、4個のFPGAで構成された負荷に、電源電圧1.5V、負荷電流40Aを供給することだった。供給電力は60Wに達する。

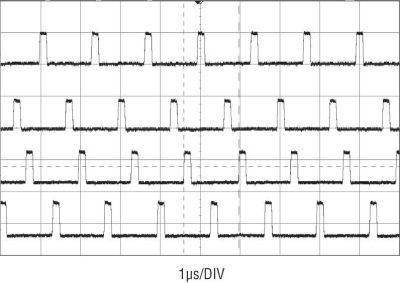

外付け部品がわずかで設計が容易

図2に例示した回路は、出力電圧1.5V、最大48Aの負荷電流を供給する。LTM4601を4つ使うことで、4×12Aの出力を供給する。これらのDC-DCコンバータ回路は互いに同期しているものの、互いに90度ずつずらして動作させているので(図3)、相殺効果によって入力と出力に含まれるリップル電流を減らせる。位相をずらして動作させることにより、ピーク入力電流とピーク出力電流が、デューティーサイクルに依存するものの、約20%減少する。リップル電流を抑制できると、外付けコンデンサの電流定格と寸法を減らせるため、部品コストと基板面積を削減できることになる。

図2の例では、DC-DCコンバータ回路間の同期と位相シフトは、シリコン発振器「LTC6902」が担当した。この発振器は、4つの基準信号を出力し、それぞれの位相は90度ずつシフトしている。

LTM4601のPLL入力端子にシリコン発振器の基準信号を入力する。LTM4601のPLL回路は、位相検出器と電圧制御発振器で構成しており、最大850kHzの周波数の基準信号の立ち上がりにロックさせることができる。少なくとも、波形の幅が400nsで振幅が2VのパルスがPLL端子に入力されると、PLL回路は動作する。

図3 DC/DC μModuleレギュレータのリップル雑音を抑える工夫 各DC/DC μModuleレギュレータのスイッチング波形である。横軸は時間。縦軸は出力電流。それぞれの位相を90度ずらすことで、リップル雑音を抑制している。

出力電圧は外付け抵抗値で設定

出力電圧を設定するには、外付け抵抗を1つ使う。DC-DCコンバータ回路を並列に構成するときは、抵抗値は並列にした数に依存する。LTM4601を並列にすると、内部帰還抵抗の等価抵抗値が変わるからだ。

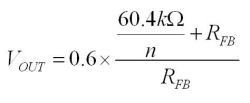

出力電圧(Vout)と、出力電圧設定用の外付け抵抗(RFB)の関係式は、以下の(1)式の通りである。

ここで、0.6は、LTM4601のリファレンス電圧の値、60.4kΩは内部帰還抵抗の値、nは並列接続したLTM4601の個数である。

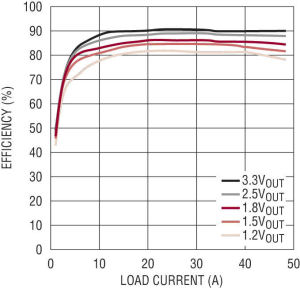

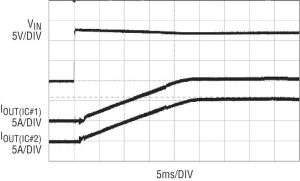

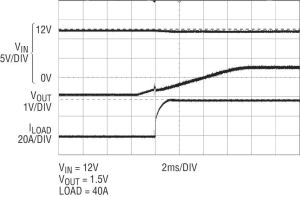

図4に、負荷電流に対する変換効率を示した。広い負荷電流範囲に渡って、高い変換効率が得られていることが分かる。図5にソフトスタート機能の効果、図6に並列接続したLTM4601がそれぞれ10A(合計20A)まで上昇するときの出力電流を示した。図6から分かるように、並列接続したDC-DCコンバータ間で、起動時から最大負荷に至るまで、十分にバランスの取れたカレントシェアリングが実現できる。

図5 ソフトスタート機能の効果 横軸は時間、縦軸の上のラインは入力電圧、中央のラインは出力電圧、下のラインは負荷電流。出力電圧の立ち上がりがゆるやかになっている様子が分かる。FPGAやシステム全体を適切に駆動させるには、制御されたソフトスタートが必要。

Copyright © ITmedia, Inc. All Rights Reserved.