電源電圧0.6Vの基準電圧源IC、非対称な2つのMOSFET構造で実現:アナログ設計

1.0Vを切るような低い電源電圧で動作する基準電圧源ICが登場した。リコーが発表したもので、電源電圧は0.6V、消費電流は1.7μA、温度に対する出力変化は106ppm/℃である。

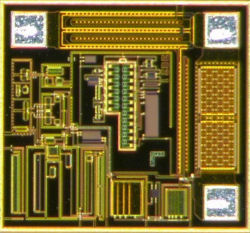

1.0Vを切るような低い電源電圧で動作する基準電圧源ICが登場した(図1)。リコーが発表したもので、電源電圧は0.6V、消費電流は1.7μA、温度に対する出力変化は106ppm/℃である。このデータは学会で発表したいわゆるチャンピオンデータだが*1)、現在同社は量産に向けた取り組みを進めている。2011年には、電源電圧が1.0V以下の基準電圧源ICを製品化する予定だ。

基準電圧源ICは、さまざまな電子回路の動作を下支えする重要なICである。特に、アナログ回路は扱う信号の状態が連続的に変化するため、温度や製造ばらつき、外来雑音に対して安定した基準電圧を供給することが重要になる。

さまざまな電子回路の低電源電圧化の流れを背景に、基準電圧源ICの電源電圧の引き下げが求められていたものの、なかなか進んでいなかったという。「電源電圧が1.0V以下ならば、低電源電圧化の進んだシステムの中でも基準電圧源ICを他の回路に先んじて起動できる。先に他の回路が立ち上がると、基準となる電圧が得られないため、動作が不安定になる可能性がある」(同社の電子デバイスカンパニー 新規技術開発室のエグゼクティブスペシャリストである渡辺博文氏)。

図1 リコーが開発した電源電圧0.6Vの基準電圧源IC 基準電圧を生成する回路構成や、回路に使うMOSFETの素子構造を工夫することで、電源電圧を1.0Vを切るレベルにまで引き下げた。消費電流は1.7μA、温度に対する出力変化は106ppm/℃である。出典:リコー

従来手法には課題あり

基準電圧源ICを実現するのには、いくつかの方法がある。代表例が、(1)BGR(Band Gap Reference)回路や、(2)2つのMOSFETの立ち上がり電圧Vthの差を使った基準電圧生成回路である。しかし、いずれの方法も、低電源電圧化するのには原理的な課題を抱えているという。

(1)のBGR回路は、一般にバイポーラトランジスタのベース-エミッタ間の温度特性を利用する。この方法では、所要の電源電圧はトランジスタの材料であるシリコン(Si)のバンドギャップで決まるため、1.25V以下にするのが難しかった。

(2)の2つのMOSFETの立ち上がり電圧Vthの差を使った方法では、一般にMOSFETのチャネルの不純物濃度を変えることで、Vthの差を生み出している。電源電圧を下げようとすると、チャネルの不純物濃度を調整するのが難しくなるという課題があった。

リコーが開発した方法は、2つのMOSFETを使う点や、立ち上がり電圧Vthの差を利用して基準電圧を作り出す点は、前述の(2)の方法と同じである。違いは、基準電圧を生成する回路構成や、回路に使うMOSFETの素子構造にある。工夫したポイントは複数あるが、全体を俯瞰(ふかん)してみると、従来方法とは大きく異なる基準電圧の生成方法を開発したといえる。

「バックバイアス効果」を活用

詳しく説明しよう。まず、2つのMOSFETの立ち上がり電圧Vthの差を生み出すために、チャネルの不純物濃度ではなく、ゲートの不純物種類を変える方法を採った。例えば、2つのnチャネル型MOSFET(M1とM2)を使うとき、一方のゲートはp+型、もう一方はn+型になるように不純物を注入する。「ドレイン、ソース、チャネルの特性を、2つのMOSFETで同じにできるため、製造ばらつきに対する耐性が上がる。具体的には、2つのMOSFETのVthの差が、ゲートの仕事関数の差だけで決まるようになる」(渡辺氏)。

しかし、製造ばらつきに対する耐性は上がるものの、この方法だけでは電源電圧を1.15Vよりも下げるのは難しかった。

そこで、電源電圧をさらに引き下げるために、2つのMOSFETを組み合わせた基準電圧生成回路の構成を工夫した。M1とM2という2つのMOSFETのうち、従来はM1のソースに接続していたM1のゲートを、グラウンドに接続するというもの。「バックバイアス効果」と呼ぶ現象によって、ドレイン電流を減らすことができる。その結果、M1とM2の動作点の電圧が下がるため、電源電圧も下げられることになる。

バックバイアス効果によって、電源電圧は下げられるが、欠点もあった。バックバイアス効果を使うとMOSFETの温度特性が悪化してしまうと考えられていたのである。これでは、基準電圧源には使えない。

2つのMOS FETのチャネル長を最適化

電源電圧は下げられるが、温度特性が安定しない・・・。この問題を解決するためにリコーが考えたアイデアが、2つのMOSFETの素子構造を非対称にすることだった。2つのMOSFET(M1とM2)で構成した基準電圧生成回路の出力電圧Vrefは、以下のように表せる。

AとBは、MOSFETのチャネル長(LM1とLM2)やキャリア移動度で決まる係数である。Vthとは異なる温度特性を持ったAとBを使ってVthの温度特性を調整することで、温度変化に対してVrefを一定にしようというのが基本的な考えである。「温度変化に対してVrefが安定となる2つのMOS FETのチャネル長の比を、比を変えたさまざまな試作を使った実験で決定した」(渡辺氏)。LM1/LM2=0.5のとき、温度変化に対してVrefが最も安定になるという。

同社では、2001年〜2008年の期間、上に説明した要素回路(セル)の開発に注力してきた。基礎的な技術開発は完了し、2010年には低電圧駆動のオペアンプをセルに組み合わせてIC化することに成功した。

Copyright © ITmedia, Inc. All Rights Reserved.