FPGA大手ベンダーのアルテラは、組み込み機器の市場に向けた取り組みを強化すると発表した。組み込み用マイクロプロセッサとFPGAを組み合わせるシステムを、容易に構築できる環境の実現を目指す。FPGAをマイクロプロセッサのソフトウエア処理負荷を軽減(オフロード)するハードウエアアクセラレータとして動作させる。「組み込み市場では、消費電力の制約から、マイクロプロセッサにリコンフィギュラブルな(FPGAによる)アクセラレータを組み合わせる手法がトレンドになっており、その組み合わせの多様化が求められている。今回の取り組みは、これに応えるものだ」(同社のプロダクト&コーポレート・マーケティング担当バイスプレジデントを務めるVince Hu氏)(図1)。

具体的には、大きく3つの取り組みを進めていく。1つ目は、組み込みプロセッサベンダーとの提携関係を確立すること。2つ目は、プロセッサのソフトウエア開発環境とFPGAのハードウエア開発環境を連携させて両者の開発とデバッグに対応できる環境を構築すること。3つ目は、プロセッサとFPGAを接続するインターコネクトの設計を支援するソフトウエアツールを整備することである。これらの一連の取り組みを同社は「エンベデッド・イニシアチブ」と呼ぶ。

ARMやMIPS、AtomをFPGAと統合

1つ目に掲げたプロセッサベンダーとの提携関係の確立では、ユーザーである組み込み機器の設計者に、アルテラのFPGAと組み合わせるプロセッサの選択肢を数多く提供できるようにする。すでに、組み込み向けプロセッサを手掛けるアームとインテル、ミップス・テクノロジーズそれぞれと提携を結んでおり、今後、各社のプロセッサとFPGAの統合を進める。

統合の進め方は具体的にはこうだ。アームとミップスについては、アルテラが両社からプロセッサコアIPのライセンス供与を受けて、FPGAユーザーにソフトIP形式で提供するほか、ハードIP形式であらかじめFPGAに集積して供給する。28nm世代のプロセス技術で製造する次世代FPGAで、アームの「Cortex-A9」コアをハードIP形式で集積した品種を用意する計画だ。またアームの「Cortex-M1」コアについては、すでにソフトIP形式で提供を始めている。さらに、ミップスの「MP32」コアについても、ソフトIP形式で提供することを2009年に発表済みだ。

インテルについては、現時点ではアルテラがFPGAをインテルに供給する形の提携関係を結んでいるという。すでにインテルが、2010年9月中旬に開催した開発者会議「Intel Developer Forum 2010(IDF 2010)」で、同社の組み込み向けプロセッサ「Atom」とアルテラのFPGAをマルチチップパッケージ技術で1個のパッケージにまとめた「Stellarton」を発表済みである。

なおアルテラが独自に開発し、従来から提供していたソフトIP形式のプロセッサコア「Nios II」については、「当社の既存ユーザーの30%以上が利用している」(同氏)ほど普及しており、今後も提供を続けるという。

取り組みの2つ目に掲げたプロセッサのソフトウエア開発環境とFPGAのハードウエア開発環境の連携については、「提携関係にあるプロセッサベンダー各社と協力し、設計フローの強化を進める」(同氏)と表明した。

高性能インターコネクト自動生成ツールを新たに提供

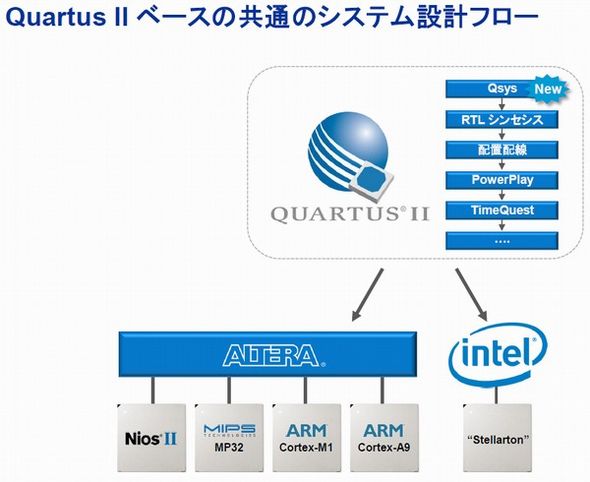

3つ目に掲げた、プロセッサとFPGA間のインターコネクト設計支援ツールの整備では、アルテラのFPGA開発環境「Quartus II」に、インターコネクト自動生成ツール「Qsys」(キューシスと発音する)を新たに組み込んだ(図2)。FPGAに実装するユーザーロジックとプロセッサをつなぐインターコネクト回路のRTLコードを自動的に生成するツールである。アルテラがこれまで、Nios IIコアを実装するFPGAの開発環境として提供していたツール「SOPC Builder」の後継と位置付ける。

Qsysでは、FPGAに最適化したネットワークオンチップ(NoC)技術を採用した。インターコネクトの性能をSOPC Builderに比べて最大2倍まで高められるという。「SOPC Builderを利用する場合、インターコネクトの性能を高めるには、ユーザーが手作業でパイプラインを挿入しなければならなかった。Qsysではこれを自動化した」(同氏)。このほかQsysは、「AMBAをはじめとした業界標準のIPインターフェイスもサポートする」(同氏)という。すでにβ版を複数の先行ユーザーが使用しており、2010年末までに一般ユーザーにも提供を開始する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.