ザイリンクスは、28nm世代の半導体プロセス技術で製造する次世代FPGA「Xilinx 7シリーズ」に3次元パッケージ技術を採用したと発表した。単一のパッケージに複数のFPGAチップを収めることで、ロジックセルや高速シリアルトランシーバ、組み込みメモリなどのパッケージ当たりの集積度を大幅に高める狙いだ。

最初に、7シリーズのハイエンドファミリ「Virtex-7」の最大規模品である「Virtex-7 2000T」にこの技術を適用する。ロジックセル数は200万個に達し、10.3Gビット/秒動作の高速シリアルトランシーバを36チャネル搭載するという。「これまで複数枚のASICやASSPを組み合わせて構築していた機能を、1パッケージのFPGAで実現できるようになる」(同社でシニア マーケティング マネージャを務めるDavid Myron氏)(図1)。

図1 28nm世代品のパッケージ技術を発表するザイリンクス首脳陣

2010年10月に東京都内で報道機関向けの発表会を開催した。左がシニア マーケティング マネージャのDavid Myron氏、右が上級副社長兼CTOのIvo Bolsens氏である。

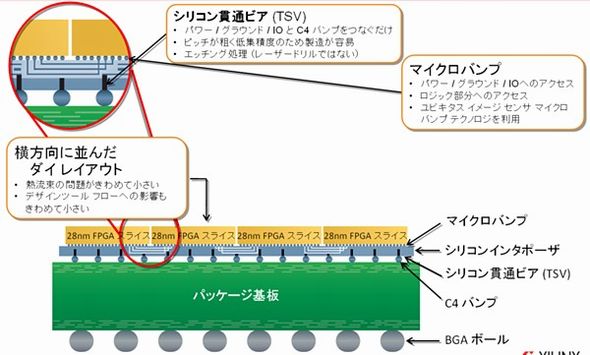

同社はこの3次元パッケージ技術を「スタックド シリコン インターコネクト」と呼ぶ。樹脂材料を使うパッケージ基板の上に、Si(シリコン)材料を使った支持基板(インターポーザ)を載せ、その上にFPGAのベアチップを複数枚、同一平面に並べて実装する構造である(図2)。複数のFPGAチップを縦方向に積層して実装するわけではない。FPGAチップ同士は、Siインターポーザを介して信号をやりとりする仕組みだ。

Siインターポーザは、4層の金属配線層を備え、厚みは100μmと薄い。トランジスタなどの能動素子は一切搭載していない、完全に受動(パッシブ)型の支持基板だ。FPGAチップを相互につないだり、パッケージの外部I/O端子に接続したりするインターコネクトだけを作り込んである。インターポーザとパッケージ基板との間は微小なはんだバンプで接続した。金属配線とはんだバンプの接続には、シリコン貫通電極(TSV:Through Silicon Via)を用いる。インターポーザとFPGAチップとの間は、さらに小さなマイクロバンプで接続した。

図2 スタックド シリコン インターコネクトの構造

Si(シリコン)材料を使うインターポーザの上に、やはりシリコンのFPGAチップを積層する構造を採る。同じ材料で熱膨張係数に差が無いため、マルチチップ品ながら高い信頼性を確保できるという。

移行初期の微細化プロセスでも集積度を高められる

ザイリンクスが今回、このようなパッケージ技術を採用した背景には大きく2つの課題がある。

1つは、製造プロセス技術の微細化を進めた当初は、大規模なチップを製造しにくいという課題である。通常、半導体チップの歩留まりはチップ面積が大きくなるほど低くなる。また一般に、半導体プロセス技術は、時間の経過とともに成熟して製造歩留まりが向上する。つまり、微細化を進めた当初は、面積が比較的小さいチップでなければ十分な歩留まりが得られない。

そこでザイリンクスは、チップの面積を大きくとることで集積度を高めるのではなく、比較的小さいチップを複数枚、単一のパッケージに収める手法を採ることで、移行初期の微細化プロセスでも集積度を高められるようにした。例えばこのパッケージ技術を適用する製品の第1弾となる前述のVirtex-7 2000Tでは、比較的小型のFPGAチップを4枚組み合わせており、ザイリンクスの現行品である40nm世代のFPGAで高速シリアルトランシーバを内蔵した最大規模の品種に比べて、ロジックの集積度が3.5倍以上に高まるという(図3)。競合他社が発表済みの28nm世代品で高速シリアルトランシーバを集積する品種に比べても、「ロジック集積度は2.8倍だ」(同氏)と主張する。

マルチチップ接続で費やされる電力を大幅に低減

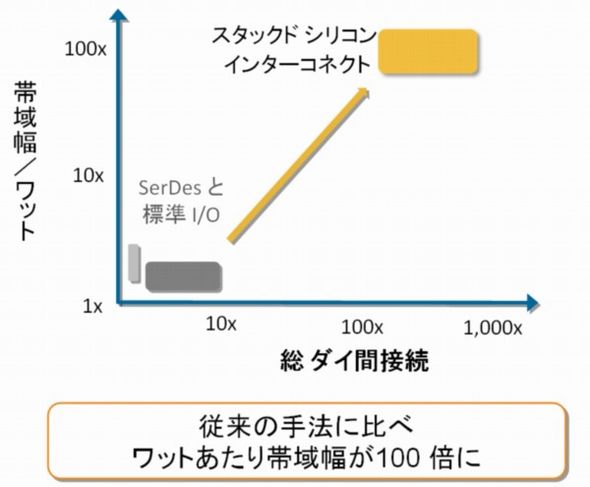

もう1つの課題は、従来のマルチチップ技術では、消費電力の増大を抑えつつ入出力帯域幅を拡大できないことである。

プリント基板上で複数のFPGAを組み合わせる手法では、FPGAチップ間を標準の入出力や高速シリアルトランシーバで接続する。こうしたインターフェイスは、信号の振幅が比較的大きい上に、FPGA間の配線が比較的長いので静電容量も大きい。従って、大きな電力を消費してしまう。また、配線による信号の遅延が比較的大きい点も問題だった。樹脂材料のインターポーザを利用する従来のマルチチップモジュール(MCM)でも、プリント基板上で組み合わせる場合に比べれば消費電力や遅延を比較的小さくできるものの、無視できない大きさであることは変わらない。

これに対し今回のザイリンクスのパッケージ技術では、先に述べた通りSiインターポーザを採用し、チップ間の配線距離を大幅に短縮した。さらに、パッケージの外部端子につながる入出力を除き、パッケージ内部でFPGAチップとFPGAチップをつなぐ入出力は、チップ内部でノードとノードを接続する入出力とまったく同じ回路構成にしたという。つまり、チップ間で信号を入出力しても、消費電力はチップ内で信号をやりとりする場合とほとんど変わらない程度に抑えられる。遅延についても、チップをまたぐ接続で約1nsと短いという。

しかも、これらの入出力は外部端子に接続しないため、単位面積当たりの端子密度を大幅に高められる。消費電力を増大させることなく入出力帯域幅を拡大できるというわけだ(図4)。実際に、「パッケージ内部では、FPGAチップ間を1万本以上のインターコネクトで接続している」(同氏)という。

ユーザーのFPGA開発手法は変わらない

このように新たなパッケージ技術を採用しながらも、FPGAユーザーが独自の回路を設計して実装する手法は旧来と変わらないという。「複数枚のチップを単一パッケージに収めながらも、FPGAユーザーが設計する際には、あたかも1枚の大規模なFPGAのように見える」(同氏)。タイミング収束の手法や、全体的な設計フローも従来通りだと説明している。

ただし、複数枚のチップに明示的に回路や信号経路を割り当てられるフロアプラン作成機能も用意する。これを利用すれば、さらに高い性能を引き出すことが可能だ。

今回の3次元パッケージ技術を適用した最初の製品となるVirtex-7 2000Tは、すでに限定的な顧客企業に試作品の提供を始めており、2011年の半ばにエンジニアリングサンプル品の出荷を始める予定である。開発ツールについては、同社のFPGA統合開発環境である「ISE Design Suite」の「13.1」版でこのマルチチップ品に対応する。すでにこのベータ版を、試作品を利用する顧客企業に提供しているという。

Copyright © ITmedia, Inc. All Rights Reserved.