アルテラが28nm FPGAの追加情報を公開、低コスト品や高速シリアル品の全容明かす:プログラマブルロジック FPGA

同社は2010年4月にハイエンドファミリ「Stratix V」の製品概要を公開していた。今回はハイエンド品の仕様の拡張点を明らかにした他、28nm世代で別に用意する複数の製品ファミリの概要も公開した。

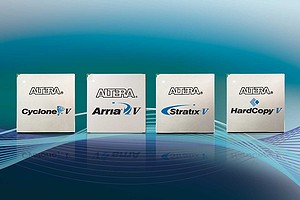

FPGAの大手ベンダーであるアルテラは、2011年1月25日、28nm世代の製造技術を適用する次世代FPGA群の製品構成を発表した(図1)。

図1 アルテラの28nm製品群 左から順番に、低コストファミリ「Cyclone V」、ミッドレンジファミリ「Arria V」、ハイエンドファミリ「Stratix V」、ストラクチャードASIC「HardCopy V」である。出典:日本アルテラ

同社は、2010年2月に28nm世代のFPGAに適用する新技術について公表し、同年4月にハイエンドファミリ「Stratix V(ストラティクス・ファイブ)」の製品概要を公開していた。また同年12月には、28nm世代のプロセス技術戦略を発表し、4月の時点で公表していた通りハイエンドファミリにTSMC(Taiwan Semiconductor Manufacturing Company)の「28nm High Performance(HP)」プロセス技術を適用するという方針に加えて、低コストファミリとミッドレンジファミリにTSMCの「28nm Low-Power(LP)」プロセス技術を適用することを新たに表明していた。

今回の発表では、ハイエンドファミリの製品仕様の拡張点を明らかにした他、28nm世代で別に用意する複数の製品ファミリの概要も公開した。

高速シリアルトランシーバの仕様拡張でOTN対応を強化

ハイエンド品のStratix Vについては、すでに詳細なファミリ構成を開示しており、それ自体に大きな変更は無い。出荷スケジュールについても、従来発表していた通り、2011年の第1四半期にエンジニアリングサンプル品を出荷するという予定に変更は無いという。今回は、これまで公表していた仕様のうち、高速シリアルトランシーバの動作速度を高めたことを発表した。

すでに発表していた通り、Stratix Vでは2種類の高速シリアルトランシーバを用意しており、想定する応用分野が異なる4つのサブファミリごとに、集積する高速シリアルトランシーバの種類やチャネル数を変える。より高速な種類は最大28Gビット/秒で動作し、これは従来の発表通りだ。今回、動作速度の仕様を高めたのは2種類のうち比較的低速の方で、従来は最大12.5Gビット/秒としていたが、これを最大14.1Gビット/秒まで引き上げた。この仕様の拡張によって、「OTN(Optical Transport Network)分野の応用範囲が広がる。例えば、16Gビット/秒のファイバチャネル(Fibre Channel)の物理層における伝送速度である14.025Gビット/秒にも対応可能になった」(アルテラでプロダクト・マーケティング担当シニア・ディレクタを務めるDavid Greenfield氏)という(図2)。

低コスト品と高速シリアル品、ストラクチャードASICの全容も明らかに

28nm世代では、ハイエンドファミリの他に、3つの製品ファミリを用意する。すなわち、幅広い用途に向けて低コストを重視したファミリ「Cyclone V(サイクロン・ファイブ)」と、高速シリアルトランシーバを集積しながらもコストを比較的低く抑えたミッドレンジファミリ「Arria V(アリア・ファイブ)」、ストラクチャードASIC「HardCopy V(ハードコピー・ファイブ)」である。アルテラは今回、これら3ファミリの製品概要も明らかにした。

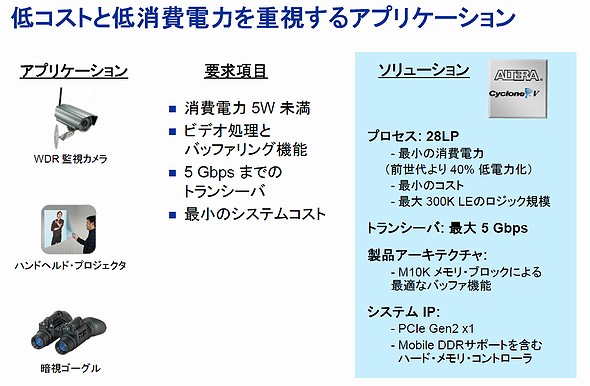

低コストファミリのCyclone Vは、監視カメラや携帯型プロジェクタ、暗視ゴーグルなど、低コストとともに低消費電力が強く求められるアプリケーションを想定する(図2)。2010年12月に発表した通りTSMCの28nm Low-Powerプロセスで製造することで、「前世代品に比べて消費電力を40%低減でき、5W未満に抑えられる」(アルテラのGreenfield氏)という。以下は、現時点での暫定版の仕様である。ロジック・エレメントの集積規模は最大規模品で30万個、最小規模品で2万5000個。5Gビット/秒動作の高速シリアルトランシーバを最大12チャネル、DSPブロックを最大385個、PCI Express 2.0コントローラを最大2チャネル、それぞれハードマクロとして集積する。2012年の第1四半期に最初のチップを出荷する計画だ。

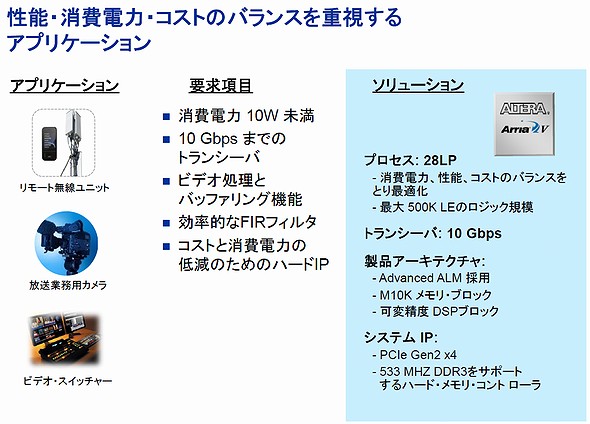

ミッドレンジファミリのArria Vは、携帯電話基地局の高周波送受信部を独立ユニット化したいわゆるリモートラジオヘッド(RRH)の他、放送業務用カメラやビデオスイッチ装置など、「性能と消費電力、コストのバランスが重視されるアプリケーションに向けて最適化した」(Greenfield氏)(図4)。低コストファミリと同様にTSMCの28nm Low-Powerプロセスを適用するが、コストと消費電力に性能を加えた3つの要素のバランスをとりながら設計を最適化したという。

高速シリアルトランシーバについては、6Gビット/秒動作と10Gビット/秒動作の2つを用意しており、両方を混載するサブファミリ「Arria V GT」と、6Gビット/秒版のみを搭載する「Arria V GX」をラインアップする。以下は現時点での暫定版の仕様である。Arria V GTは6Gビット/秒版を最大24チャネルと10Gビット/秒版を最大6チャネル、Arria V GXは6Gビット/秒版のみを最大36チャネル集積する。両サブファミリともに、ロジック・エレメントの集積規模は最大規模品で49万5000個、DSPブロックは最大1139個である。PCI Express 2.0コントローラは4レーン(×4)対応版をArria V GTは1チャネル、Arria V GXは最大2チャネル集積する。2011年の後半に最初のチップを出荷する計画だ。

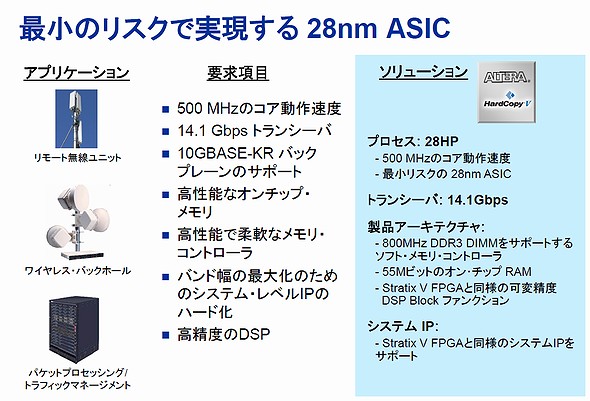

ストラクチャードASICのHardCopy Vは、ハイエンドファミリと同様に、TSMCの28nm High Performanceプロセスで製造する(図5)。コアロジック部の動作周波数は最大500MHzと高く、ハイエンドファミリの350MHzを上回る。ただし想定する用途は、ハイエンドファミリのASIC化ではない。「量産数量の多い用途を想定している。実際には、まず低コストファミリであるCyclone Vで設計し、大量生産を開始するタイミングでHardCopy Vに移行するといった使い方が主流になるだろう」(Greenfield氏)と説明する。

このため、高速シリアルトランシーバについては、ハイエンドファミリが集積する28Gビット/秒版には対応せず、14.1Gビット/秒版までの対応とした。「HardCopy Vが利用される主な用途は、10Gビット/秒程度のデータ伝送速度が中心になる。従って、28Gビット/秒版をストラクチャードASICのマスタースライスに集積してしまうと、不要なコスト負担をユーザーに強いることになってしまう」(同氏)。具体的な用途としては、リモートラジオヘッドの他、モバイルバックホール(数多くの携帯電話基地局を収容してモバイルコアネットワークにつなぐアクセス網)用装置や、パケット処理/トラフィック管理装置などを挙げている。

なおアルテラは今回、FPGA開発ツール「Quartus II」の28nm世代製品群への対応スケジュールについても明らかにした。Stratix Vについてはすでにサポートを始めており、他のすべての製品群についても2011年中にサポートを開始する計画だという。

Copyright © ITmedia, Inc. All Rights Reserved.