米国のサンフランシスコで2011年2月20日〜24日に開催された半導体回路技術の国際学会「ISSCC(IEEE International Solid-State Circuits Conference) 2011」。本稿は、ISSCC 2011におけるこれらの発表の中から、12の技術を写真とともに紹介するフォトギャラリーの後編である。なお写真のほとんどは、今回のISSCCから新たに設けられた実演イベント「Industrial Demo Session」で撮影したものだ。

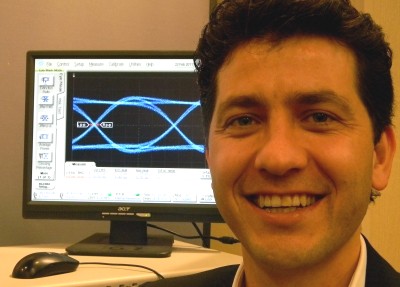

銅線にも光ケーブルにも対応するネットワークチップ

ファブレス半導体企業であるNetLogic Microsystemsでミックスドシグナル設計担当のシニアエンジニアを務めるHalil Cirit氏は、40nmのプロセス技術で製造した10Gビット/秒対応イーサネットチップを展示した。「10Gbase-KR」規格の銅線ケーブル接続と、光トランシーバの規格である「SFP(Small Form factor Pluggable)+」の光ファイバ接続それぞれで信号を伝送し、どちらでもきれいなアイパターンが得られることをアピールして見せた。10Gビット/秒対応イーサネットの市場は、今まさに立ち上がり始めているところだ。現在は、光ファイバのみの接続から、光ファイバと銅線の両方を使った接続への移行期にある。Cirit氏が今回のISSCCで発表したこの低ジッターチップは、すでに量産が始まっている。

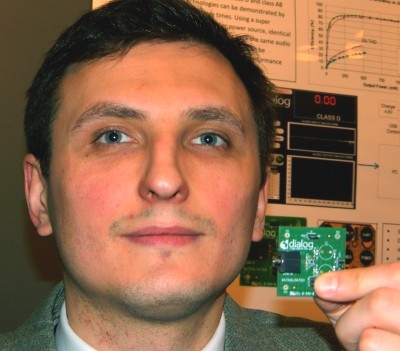

D級アンプのノイズを低減

Dialog SemiconductorのD級オーディオアンプは、3.6Wのオーディオ出力でTHD+N(全高調波歪み+ノイズ)が0.0012%と低い。シニア設計エンジニアのMykhaylo Teplechuk氏は、ISSCCで発表したこの4mAのチップを 披露した。このチップは、皆さんが将来手にするMP3プレーヤーに搭載されるかもしれない。

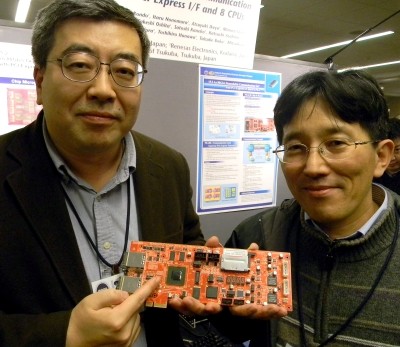

PCI Expressの新たな応用を開くチップ

筑波大学大学院のシステム情報工学研究科でコンピュータサイエンス専攻の教授を務める朴泰祐氏(写真左側)と、ルネサス エレクトロニクスでプロセッサ開発部門の部長を務める近藤弘郁氏(同右側)は、PCI Expressの新しい応用を開く共同研究プロジェクトのメンバーである。このプロジェクトで開発したSoCの試作チップは、PCI Express Gen2を4リンクと、ルネサスのプロセッサコアを4つ、1枚のスイッチングチップに集積している。

このチップは、単一のマスタープロセッサにしかリンクできないという従来のPCI Expressの制約を打ち破り、2つのCPUをノードとしてアドレスできる。この新手法によって、イーサネットやCANスイッチよりもパワフルでありながら、インフィニバンドをベースとする場合よりも低いコストで、幅広い範囲の通信システムや自動車システムを実現できるようになるという。

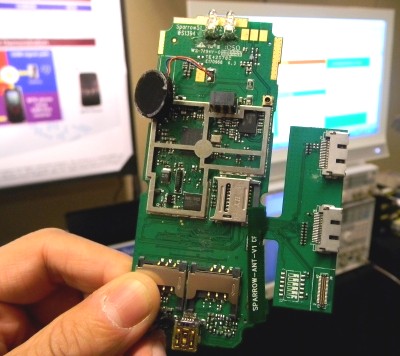

携帯用SoCの外付けフィルタが不要に

MediaTekは今回のISSCCで、GSM/EDGE対応の携帯電話機に向けた1チップレシーバを発表した。このチップは、従来は不可欠だった4個の外付けSAWフィルタを不要にしており、携帯電話機の設計をよりシンプルにできる。半導体業界では今、中国や世界各地の新興国市場に向けて、チップやシステムをシンプルにする取り組みを数多くの企業が進めており、MediaTekもその中の1社である。

Copyright © ITmedia, Inc. All Rights Reserved.