【iPad 2分解・続報】メインプロセッサ「A5」、従来品「A4」に続きサムスンが製造:製品解剖 タブレット

UBM TechInsightsは、アップルの新型タブレット「iPad 2」の本体とチップを分解した結果を発表した。それによると、iPad 2に搭載されているプロセッサ「Apple A5」は、サムスン電子が製造したものだという。

UBM TechInsightsは、アップルの新型タブレット「iPad 2」の本体とチップを分解した結果を発表した。それによると、iPad 2に搭載されているプロセッサ「Apple A5」は、サムスン電子が製造したものだという。なおUBM TechInsightsは、米EE Times誌と同じくUnited Business Media傘下の技術情報サービス企業である。

UBM TechInsightsでテクニカルマーケティングマネジャーを務めるAllan Yogasingam氏は、「A5プロセッサはサムスン電子が製造していると100%断言できる」と語った。

同氏によると、チップの断面分析を詳細に行った結果、A5プロセッサはサムスン電子の45nmプロセスで製造されたものだと分かったという。前世代の「A4」プロセッサと同じファブとプロセスである。業界ではiPad 2の発表以前、アップルが社内で設計したA5プロセッサの製造をサムスン電子ではなくTSMCに委託するという情報が飛び交っていた。

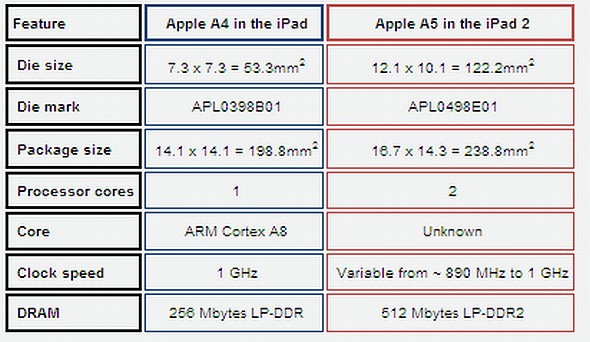

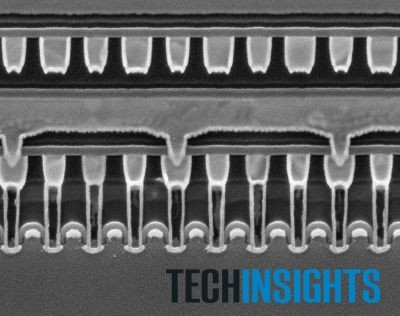

アップルのA4プロセッサとA5プロセッサはいずれも、サムスン電子の45nmプロセス技術で製造されており、9つの金属配線層と1つのポリシリコン層を備える。UBM TechInsightsによると、両プロセッサともに、PoP(Package-on-Package)技術を使ってメモリチップを積層したSoC(System on Chip)である。両チップの違いを表1にまとめた。

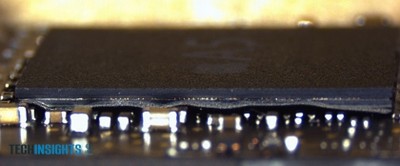

UBM TechInsightsは、可視光画像とSEM(走査型電子顕微鏡)による断面画像を撮影し、ダイのエッジシールや第1金属配線層のピッチ(配線間隔)、ロジック回路用トランジスタやSRAM用トランジスタのゲート長といった重要な特性を分析した。続いて、これらの特性を、同社のデータベースに納められている他の半導体メーカーのデータと比較した。このデータベースには、サムスン電子の他の45nmチップのデータも納められている。

この結果、A5プロセッサでは以前から予想されていた通り、LP(Low Power)DDR2 DRAMをサポートしていることが確認された。なお同社が米国のオースチン(Austin)とカナダのオタワ(Ottawa)の2つの拠点でそれぞれ分解を実施したところ、サムスン電子とエルピーダメモリという2つの異なるメーカーが生産した2つの異なるLPDDR2 DRAMが確認できた。

サムスン電子の「K4P2G324EC」というLPDDR2 DRAMのダイに刻まれた印は、46nmプロセスで製造したサムスン電子のLPDDR2 DRAMにおいて、アナリストが初めて目にしたものである。

iOS搭載デバイス専門のニュースサイトである「iOSnoops」が実施した別の分析の結果、アップルのA4プロセッサは常に1GHzのクロック周波数で動作していたが、A5プロセッサは実行するアプリケーションによってクロック周波数が変わることが判明している。UBM TechInsightsによると、この分析結果はA5プロセッサに新しい機能として、プロセッサコアのクロック周波数を制御する高度な電力管理回路が搭載されていることを示すものだという。iPad 2は、従来のアップル製品とは異なり、電力管理ICにDialog Semiconductorのチップを採用しているが、この新たな電力管理機能がその理由かもしれない。

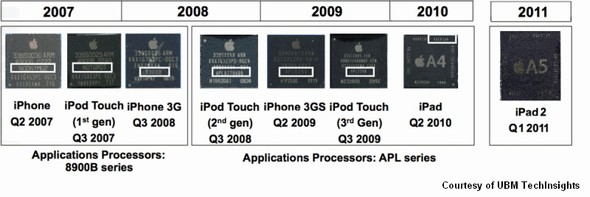

下に示す図1は、A5プロセッサのダイ上の刻印である。このチップがサムスン電子によって製造されたことを示す最も重要な印だ。この刻印のフォントは、アップルのA4プロセッサで使われたフォントに酷似している。

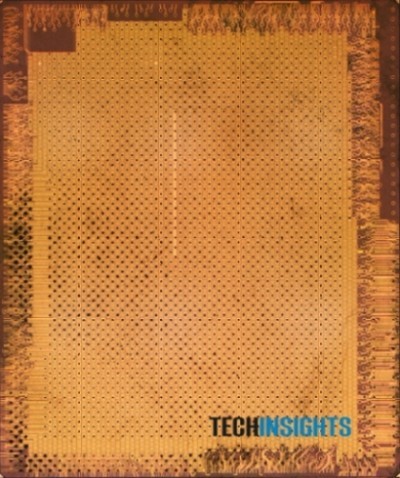

本稿ではさらに、米EE TimesがUBM TechInsightsから提供を受けたA5の写真3点と(図2、図3、図4)、アップルの従来のSoCとA5を比較した図もご覧いただこう(図5)。

図2 A5ダイの全体写真 出典:UBM TechInsights UBM TechInsightsのシニアテクニカルアナリストであるRobert Widenhofer氏によれば、A5プロセッサはダイサイズが12.1mm×10.1mmと大型だという。出典:UBM TechInsights

Copyright © ITmedia, Inc. All Rights Reserved.