モバイルインターネットが急拡大、帯域幅の危機に半導体業界が挑む:無線通信技術 LTE

モバイル端末からのインターネット利用が世界中で急激なスピードで拡大し、ネットワークの帯域幅を大量に消費し始めた結果、帯域幅が逼迫し始めている。その解決に向けた提案が半導体業界から相次いでいる。

2011年1月、アフリカのチュニジア共和国で政変が発生し、23年間にわたって続いていた独裁政権が崩壊した。そのきっかけを作ったのは「Facebook」と「Twitter」。インターネットのソーシャルサービスだった――。

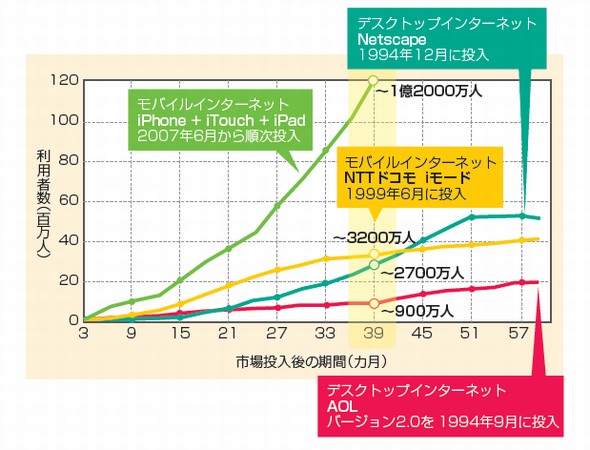

モバイル端末からのインターネット利用が世界中で急激なスピードで拡大している(図1)。その動きは、地球上のあらゆる地域で政治や経済、社会の変化を引き起こし、人々に大きな影響を与え始めた。

「わずか数年前まで、チュニジアのように、国際社会から隔絶された地域で市民の人権を侵害するような事件が起きても、それに気付く人はごくわずかだった。たとえその国内にいたとしても、当局の規制を受けたメディアがそうした事態を報じないので、多くの人は知らないままでいただろう」

こう語るのは、アナログ/ミックスドシグナルICを手掛ける半導体ベンダーのインターシルでプレジデント兼CEOを務めるディビッド B. ベル(David B. Bell)氏だ。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2011」(米国カリフォルニア州のサンタクルーズで2011年3月28日〜31日に開催)における講演で述べた。

「しかし今は違う」。同氏は続ける。「ひとたびそうした事件が起きれば、その場にいる誰かが、手にしたスマートフォンで動画を撮影する。これは先進国の話ではない。先進国の多くの人が数カ月前まで世界のどこにあるかも知らなかっただろう、チュニジアのような地域での話である。そして、わずか数分後にはその動画はYouTubeやFacebookなどのインターネットサイトに投稿される。世界には今、この動画にPCやスマートフォンからアクセスできる人が何億人もいる。以前であれば公にならずに葬られていたような事件が国内に知れ渡り、革命の引き金になる。さらに、同じような問題を抱えた近隣諸国の市民の目にそれが届き、同じような行動を起こす力を与える。これは人類の歴史で今初めて、われわれの目の前でここわずか数カ月の間に起きていることだ」。

図1 いまだかつて無い速さでモバイルインターネットが普及 インターネットを利用するサービスやモバイル端末の利用者数の推移を市場投入後の経過期間に沿って示したグラフである。1990年代に登場したサービスに比べて、2000年代に始まった新たなモバイルインターネットは、過去に無い急激な速度で利用者数を伸ばしている。出典:モルガン・スタンレー(2010年11月発表)

トラフィックの急増に追い付かない

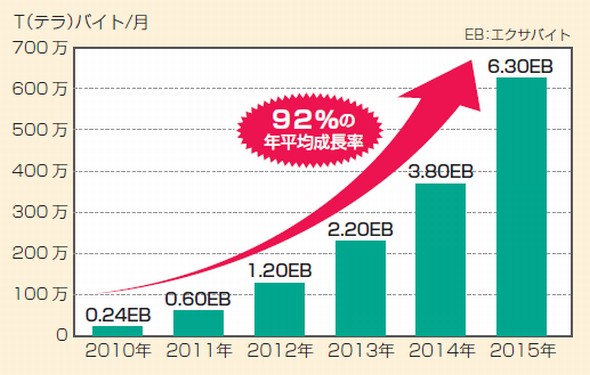

世界を変えるモバイルインターネットの技術革新。この極めて大きな潮流は、しかし、通信業界に頭痛の種をもたらしている。モバイル端末からのインターネット利用が急増し、ネットワークの帯域幅を大量に消費し始めた結果、帯域幅が逼迫(ひっぱく)し始めているのだ(図2)。

さらに米国などでは、インターネット接続対応テレビなどの固定端末に向けて映像コンテンツをストリーミング配信するサービスも普及が進んでおり、帯域幅の大量消費に追い討ちをかける。通信事業者にとっては、ネットワークインフラの帯域幅の拡大が急務だ。しかし、トラフィックの増加は速い。そのため米国では、帯域幅の拡大が追い付かないと判断した一部の通信事業者が利用者にデータ量の上限を設ける動きも出始めている。

図2 モバイルからのインターネット利用が急拡大 モバイル端末からのインターネット利用によるネットワークトラフィックは、2010年から2015年にかけて92%と高い年平均増加率で指数関数的に拡大していくと見込まれる。2011年の現在から4年後の2015年には、今の10倍を超えるトラフィックがネットワークを流れる見込みだ。出典:シスコシステムズ、Visual Networking Index(VNI):Global Mobile Data Traffic Forecast Update(2011年2月発表)

この「帯域幅の危機」にどう挑むのか。帯域幅の制約を生み出すボトルネックは、ネットワークのさまざまな部分に潜んでいる。そこでGlobalpress Electronics Summit 2011では、通信機器向け半導体を手掛ける各社が、そうしたボトルネックを取り除く解決策を提案した。通信機器向けASSPを供給するブロードコムや、FPGAベンダーのアルテラとザイリンクスなどである。

モバイルバックホールの4G移行を支援

「現在、スマートフォンやタブレットPCで大量のデータをやりとりする消費者と、通信事業者のモバイルコアネットワークの間で、帯域幅を制約する大きなボトルネックになっているのは、モバイルバックホールだ。急増するモバイルインターネットのトラフィックに対応するには、第4世代のモバイルネットワークへの移行を進める必要がある」。こう指摘するのは、ブロードコムでネットワークスイッチのプロダクトラインディレクターを務めるエドワード・ドー(Edward Doe)氏である。モバイルバックホールとは、数多くの携帯電話基地局を収容して、アグリゲーションネットワークを介してモバイルコアネットワークにつなぐアクセス網を指す。

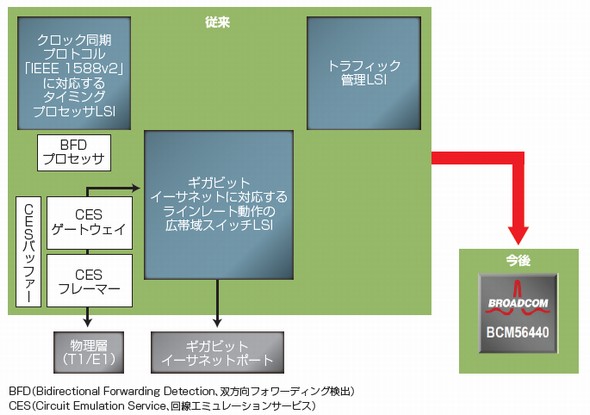

同社は、このボトルネックの解消に向けて開発した、第4世代対応のモバイルバックホール用スイッチLSI「BCM56440」を発表した。このチップは、「TMD(Time Division Multiplexing)に基づくレガシーのモバイルネットワークに比べて、1000倍の帯域幅を実現できる性能を備えている」(同氏)と主張する。

さらにBCM56440は、スイッチ機能の他にもさまざまな機能を統合しており、機器の低コスト化への要求にも応えるという。「旧来は複数のチップで構成する必要があった基地局側ルーターの主な機能を、1個のチップにすべて集積した」(同氏)(図3)。複数のチップとは、スイッチLSIの他、トラフィック管理LSIやタイミングプロセッサLSI、さらに物理層(T1/E1)とスイッチLSIの間でレガシーのTDMネットワークの回線エミュレーションサービス(CES:Circuit Emulation Service)を提供するゲートウェイとフレーマー、バッファーとして機能するチップである。ゲートウェイとフレーマー、バッファーについては、それぞれ個別の専用LSI(ASSP)を利用したり、FPGAに実装したりする手法がある。

BCM56440を使えば、これらを1チップ化できるため、「ルーター装置のコストを最大50%削減できる」(同氏)と説明した。消費電力についても、「機器のアーキテクチャによって異なるが、25%〜50%低減できるはずだ」(同氏)。入力ポートと出力ポートの構成が異なる派生品種も3つ用意しており、機器メーカーはアーキテクチャによって使い分けが可能だ。

図3 複数チップ構成の広帯域スイッチング機能を1チップに統合 以前は全て専用LSI(ASSP)で構成すると7個、一部をFPGAに集約しても4個のチップが必要だった機能を、新たに開発したスイッチLSIでは全て統合した。ルーター装置などのコストを最大50%削減できる上、消費電力についても、装置の構成によって異なるが25%〜50%低減できるという。出典:ブロードコム

3つの基本要件に応える

「モバイル端末からのインターネットの入り口になる無線データ通信を担うインフラ機器の市場には、3つの基本的な要件がある」。こう指摘するのはFPGA大手ベンダーのザイリンクスでプラットフォーム マーケティング担当ディレクタを務めるブレント・プリツバス(Brent Przybus)氏である。具体的には、「コスト当たりの性能が高いこと、消費電力が低いこと、短期間で機器を開発できることだ」(同氏)という。これらに応えることで、インフラ機器のメーカーや通信事業者は経済性を維持しながら帯域幅の拡大を進められると説明する。

同社は、28nm世代の半導体プロセス技術で製造する次世代FPGAでこれら3つの基本要件の全てに応えられると主張した。コスト当たりの性能については、40nm/45nm世代の現行FPGAであればハイエンド品「Virtex-6」が必要だった性能を、28nm世代品では価格対性能比に重点を置くミドルレンジ品「Kintex-7」で達成できるという。「Kintex-7は、45nm技術で製造する低コスト品『Spartan-6』と同等の価格帯で提供するにもかかわらず、491MHzのクロック周波数で動作し、高い処理性能を発揮する」(同氏)。

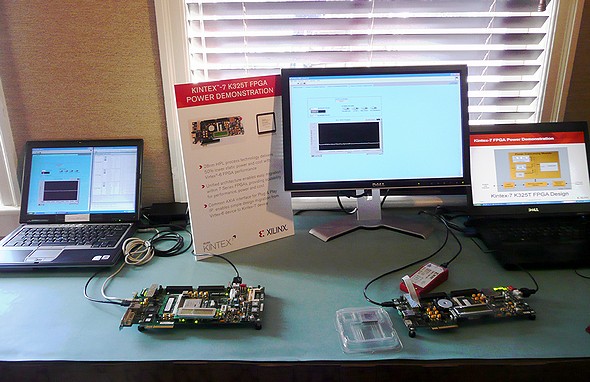

消費電力については、「放熱や冷却に必要な機構のコストや電気料金として、通信機器メーカーや通信事業者のコストに直結するため、非常に重要なポイントだ」(同氏)という。これについても、Kintex-7は現行品のVirtex-6に比べて待機時も動作時もともに消費電力を半分以下に抑えられると説明する。今回はそれを、Kintex-7のサンプルチップを使って実演して見せた(図4)。

開発期間については、28nm世代品でも、40nm/45nm世代品で導入した「ターゲット デザイン プラットフォーム」を継承する。特定のアプリケーションに向けて、IPや開発ボード、各種ドーターボード、設計ツールなどをザイリンクスが取りそろえて提供するサービスだ。「機器メーカーがこれらを独自に用意したり開発したりする必要が無いため、短期間で機器を市場に投入できる」(同氏)。

図4 待機時も動作時も電力消費は50%オフ 右側は28nm FPGA「Kintex-7」、左側は40nm FPGA「Virtex-6」をそれぞれ搭載した開発ボードである。両FPGAに同じ回路を実装して動作させ、消費電力を比較して見せた。具体的には、トグルフリップフロップを16段接続した回路を512個実装している。待機状態ではVirtex-6が1.6Wを消費するのに対し、Kintex-7は0.5Wにとどまっていた。100MHzのクロック周波数でフリップフロップ群を動作させた場合は、Virtex-6が2.1W、Kintex-7が1Wだった。

チップ自体にもボトルネックが存在

通信機器の内部でトラフィックをさばく半導体チップ自体にも、ボトルネックは存在している。その解消に向けた取り組みを発表したのがFPGA大手ベンダーのアルテラだ。同社が供給するハイエンドFPGAは、通信機器に広く使われている。同社はそのFPGAに光インタフェースを搭載する開発を進めていることを明らかにした。2011年中にサンプル品を公開する予定だという。

「通信ネットワークのインフラにも家庭向け光データ回線(FTTH)にも、すでに光通信は普及している。しかし、そうした光伝送信号を扱う装置はどうだろうか。入出力こそ光インタフェース化されているが、装置の内部では電気で信号をやりとりしているのが現状だ」(同社でICエンジニアリング担当バイスプレジデントを務めるブラッドリー・ハウ(Bradley Howe)氏)。

例えば、通信機器のラインカードに搭載されるFPGAは、内蔵の高速シリアルトランシーバ回路を介して、電気信号を使ってラインカード上のチップと通信したり、バックプレーン経由で接続する他のラインカード上のチップとデータをやりとりしたりしている。その伝送速度は、チャネル当たり10Gビット/秒超のオーダーに達する。さらにアルテラは、通信機器の帯域幅の拡張に応えるため、28nm世代のプロセス技術で製造する次世代FPGAに最大28Gビット/秒で動作する高速シリアルトランシーバ回路を集積すると発表しており、「それをさらに超える高速化にも取り組んでいく」(ハウ氏)と表明している。

そうなると問題になるのが、FPGAと他のチップをつなぐ配線である。データ伝送速度が高まるということは、信号の高周波成分が増加することを意味する。ところがプリント基板上に形成した銅配線を伝送する電気信号の損失は、周波数が高まるほど大きくなる。従ってデータ伝送速度が高まると、損失が増大し信号品位が低下してしまう。例えば、「10Gビット/秒から30Gビット/秒に高速化すると、単位長さ当たりの損失は3.5倍に増大する」(ハウ氏)。高周波特性に優れた基板材料を採用すれば、損失を同等に抑えることも可能だが、そうすると「基板のコストが5倍に膨れ上がってしまう」(同氏)ため現実的ではない。高速シリアルトランシーバ回路にも、損失の影響を補償するためにプリエンファシスやDFE(Decision Feedback Equalization)といった機能を盛り込んでいるが、今後はそれだけでは対応し切れなくなるという。「現在のような銅配線を将来にわたって使い続けることは難しい。光インターコネクトに向かうのは自明だ」(同氏)。

数十Gビット/秒で銅線置き換えへ

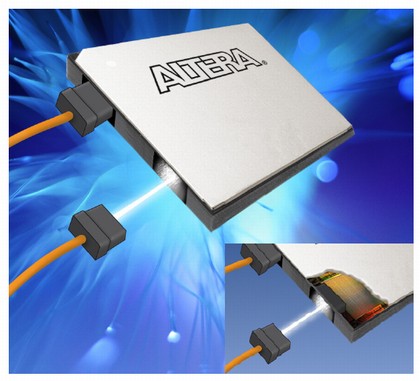

アルテラが開発中の光インタフェース搭載FPGAは、FPGAのダイに光/電気変換回路を組み合わせて単一のパッケージにまとめたものだ(図5)。光/電気変換回路の電気信号入出力側とFPGAのダイに集積した高速シリアルインタフェースをパッケージ内でつなぎ、同回路の光信号入出力側はパッケージの側面に設けた光ファイバーコネクタ用スロットに接続する構成である。

光ファイバーコネクタとしては、MPO(Multi fiber Push-On)形など、光ファイバー付きコネクタとして標準的な形状を採用する考えだ。「MPOコネクタはコストを低く抑えられるように最適化されている。それでも、現時点ではまだ電気インタフェースに比べてコストが低くなるとはいえない。しかしこれは、ニワトリとタマゴの問題だ。アップルは、インテルが『Light Peak』と呼んで開発していた光インタフェース技術を基にした新型の高速インタフェース『Thunderbolt』を搭載するノートPCを2011年2月に発表した。消費者の机の上にまで光インタフェースがやって来ているのだ。近い将来、コストの観点でも光インタフェースは電気インタフェースより有利になるだろう」(ハウ氏)*1)。

FPGAに搭載する光インタフェースの伝送可能距離については、アルテラは技術的には最大数百mを確保できるとしながらも、装置内配線(インターコネクト)用途では数mを想定していると述べている。対応するデータ伝送速度については明言していないが、「28Gビット/秒を超える領域では、銅配線による伝送が著しく困難になる。50Gビット/秒といったオーダーでは、銅配線を使えるかどうかまだ見えていない」(同社でコンポーネントプロダクトマーケティング担当のシニアディレクタを務めるルアン・シャーアイスター(Luanne Schirrmeister)氏)との見解を示した。

図5 光インタフェース搭載FPGAのイメージ アルテラが2011年中に公開すると発表した開発品のイメージである。パッケージの側面に光ファイバーコネクタのスロットを設ける。光ファイバーコネクタ自体は、MPO形などの標準的なものに対応する計画だ。出典:アルテラ

Copyright © ITmedia, Inc. All Rights Reserved.