「ムーアの法則はまだまだ継続」、Intelが3次元ゲート構造を22nmプロセスから採用:プロセス技術

Intelは、「Tri-Gate」と呼ぶ独自の3次元ゲート構造のトランジスタ製造技術を、22nm世代の製造プロセスから採用すると発表した。

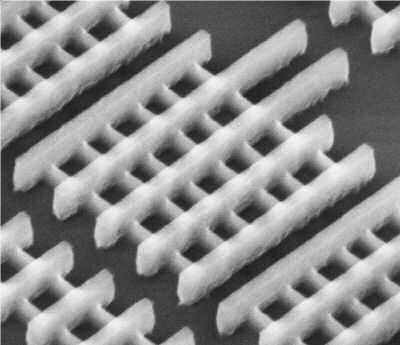

Intelは、「Tri-Gate」と呼ぶ独自の3次元ゲート構造のトランジスタ製造技術を、22nm世代の製造プロセスから採用すると発表した(図1)。22nm世代の製造プロセスによって量産するプロセッサ「Ivy Bridge(開発コード名)」から適用する。

「Tri-Gateトランジスタへの移行によって技術の進展は維持され、今後何年にもわたってムーアの法則は継続できる」(同社)という。

低消費電力と性能を両立へ

これまで何十年もの間、PCや携帯電話機、デジタル家電のみならず、さまざまな電子機器の半導体チップには、2次元ゲート構造のプレーナー型トランジスタが採用されてきた。ただ、一般的なプレーナー型トランジスタの微細化が進展するのに伴って、さまざまな物理的な限界が見えてきた。Intelが今回発表したTri-Gateトランジスタは、微細化を妨げる物理的な限界を打ち破るものだ。

Tri-Gateトランジスタでは、従来の平面的構造のゲートの替わりに、非常に薄い3次元構造の「Si(シリコン)フィン」が、シリコン基板に対して垂直に立っている。

プレーナー型トランジスタでは1つのゲートだけで電流を制御していたのに対し、Tri-GateトランジスタではSiフィンの3つの面(両側面に2つ、上面に1つ)のゲートによって電流を制御する。ゲートの電流制御能力が向上したことで、トランジスタのオン時の電流を増やし、プロセッサの処理性能を高められる。また、オフ時の漏れ電流をできる限り小さくすることで消費電力を最小限に抑え、トランジスタのオン/オフ動作を素早くできる。22nm世代の製造プロセスに基づくTri-Gateトランジスタは、従来の32nmプロセスに基づくプレーナー型トランジスタに比べて、低電源電圧時に、処理性能は最大37%向上するという。同じ処理性能で比較すると、消費電力を50%削減できる。

「さらなる微細化に伴い物理的限界が見えてきたムーアの法則を今後も維持させるうえで、3次元構造の利点を長い間、認識していた。今回の技術的ブレイクスルーによって、当社はTri-Gateトランジスタの量産化を確立し、ムーアの法則を次の世代へと継続することに成功するとともに、さまざまな電子機器にこの新技術を適用させることができる」(同社)。

Copyright © ITmedia, Inc. All Rights Reserved.