25nmプロセス適用のDRAMをエルピーダメモリが開発、7月に2Gビット品から量産開始:メモリ/ストレージ技術 DRAM

DRAM向けとしては世界最先端となる25nm世代の半導体製造プロセスを適用し、2GビットのDRAMを開発した。

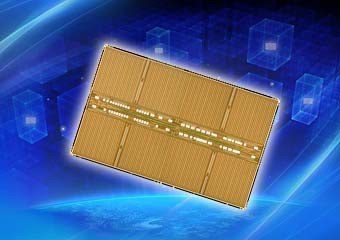

DRAM大手のエルピーダメモリは、DRAM向けとしては世界最先端となる25nm世代の半導体製造プロセスを適用し、DDR3対応の2GビットSDRAMを開発した(図1)。2011年5月2日に発表した。「世界最小のチップサイズを実現した」(同社)と主張する。2011年7月にサンプル出荷と量産を開始する予定だ。その後2011年末までに、4Gビット品の量産も始める計画である。

25nm世代のDRAMプロセスを適用することで、30nmプロセスを使う同社従来品に比べて、1ビットを構成するセルの面積を30%削減できるという。その結果ウェハー当たりのチップ取得数は、30nm世代の同社従来品に比べて、DDR3対応2GビットSDRAMで約30%、同4Gビット品で44%増加するとしている。消費電流については、30nmの従来品から動作時に約15%、待機時に約30%それぞれ低減可能だという。「PCやデジタル家電機器の消費電力低減に貢献する、エコフレンドリーなDRAMである」(同社)。

2Gビット品では、データ幅が4ビットの「EDJ2104BFSE」と8ビットの「EDJ2108BFSE」を供給する。端子当たりのデータ転送速度は1866Mビット/秒以上。電源電圧(VDD)は1.5V。動作温度範囲(TC)は0〜95℃である。1.35Vと比較的低い電源電圧で動作する品種も用意する。この低電圧品の端子当たりのデータ転送速度は1600Mビット/秒以上。なお同社は今後、携帯機器向けの製品ラインである「Mobile RAM」にもこの25nmプロセスを適用していく予定である。

Copyright © ITmedia, Inc. All Rights Reserved.