第11回 高周波出力に対応した水晶発振器を解説:水晶デバイス基礎講座(3/5 ページ)

今回は、特定の用途に向けて仕様を最適化した水晶タイミングデバイスのうち、通信機器やネットワーク機器を対象にした品種を紹介します。

n倍の高周波を出力する「周波数逓倍回路」

周波数逓倍回路とは、ある周波数の電気信号をn倍の高周波に変換する回路です。一般的な発振回路の出力信号の波形にはひずみが含まれ、きれいな正弦波を出力できません。ひずみが生じるということは、波形に高い次数の高調波が含まれているということです。周波数逓倍回路は、この高調波の中から所望のn次の高調波成分を共振させ、抽出します。

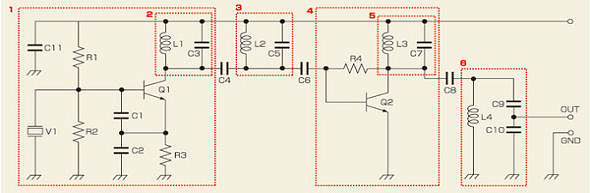

図3に周波数逓倍回路の一例を挙げました。破線1部は、水晶振動子Y1と所定の周波数で発振する発振回路を構成しています。

破線1部の後段の破線3部に示した同調回路によって、破線1部の発振出力に含まれる所定の高調波成分に同調させます。破線4部は、増幅用トランジスタQ2や自己バイアス回路で構成した増幅回路です。自己バイアス回路とデカップリング回路によって、異常発振を抑えつつ、逓倍出力を得られるように構成されています。

高調波成分を使うことでジッタの小さい出力周波数を得られますが、n次の高調波のみを抽出する回路をうまく作り込む必要があります。さらに、元信号がn次の高調波付近に雑音(スプリアス)を持たないようにするなど、水晶振動子の選定や発振回路の設計に配慮が求められます。

飛躍的に進化してきたPLL回路

高周波の安定した周波数を作り出す要素技術のもう一方のPLL回路に話題を移しましょう。無線通信機能を搭載した機器の普及に伴って、無線通信向け半導体技術は飛躍的に進歩してきました。その中でも特に、PLL回路技術の進歩は目覚ましいものがあります。現在では、PLL回路技術を応用し、次世代イーサネットに必要とされる200M〜2GHz帯の基準信号を作り出す水晶発振器が製品化されています。

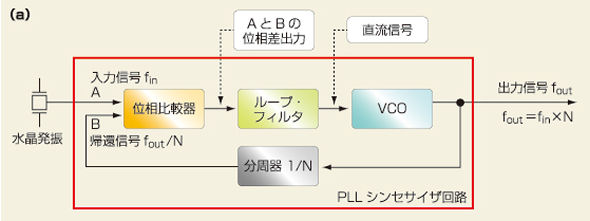

PLL回路は、入力の基準信号に同期した出力信号を発生させる回路です。位相比較器、ループフィルタ、電圧制御発振器(VCO)という基本構成で、入力信号に正確に同期した信号を生み出します(図4(a))。周波数逓倍回路とは異なり、元信号を出力に使いません。PLL回路では、元信号と周波数が異なる同期された信号をVCOによって生み出します。

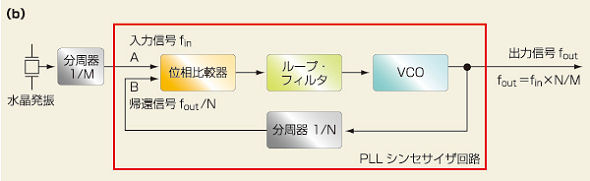

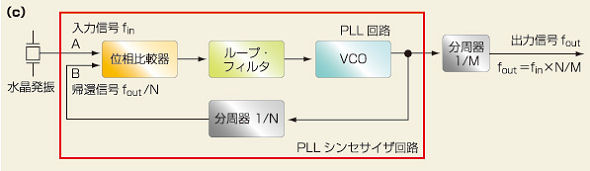

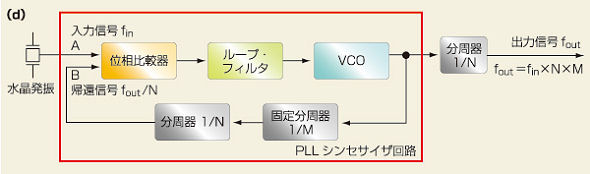

図4 PLLシンセサイザ回路の構成例 (a)は、PLLシンセサイザ回路の基本構成。(b)のように入力に分周器を挿入する例や、(c)のように出力に分周器を挿入する回路、(d)のように、VCOから分周器の間に固定分周器を追加して、入力周波数のN×M倍の出力を得る方法もある。

PLL回路のVCO出力と位相比較器への入力の間に分周器を挿入し、入力信号と分周された信号の同期により、VCOの出力は入力信号を分周数倍した周波数に制御されます。入力信号が水晶発振器などの安定したものを使い、分周器の分周数を切り替えるようにすれば、VCOの出力は水晶発振器の安定した精度と同じ確度で分周倍された信号が得られます。これが、周波数シンセサイザです。

例えば、この原理を使い、BluetoothやWi-Fiといった無線通信用途では、2.4GHz帯の搬送波を生成するために、10〜40MHzのATカット型水晶振動子を使います。10〜40MHzの出力をPLL回路に入力し、GHz帯の信号を作り出しているのです。

PLL回路を用いて入力周波数の何倍も高い周波数を作るには、この分周器の使い方が鍵になります。入力周波数のN倍の出力を得る方法は、図4(a)に示した回路構成です。さらに細かい出力の設定をするには、図4(b)のようにPLL回路の入力前に分周回路を入れる方法や、図4(c)のように出力に分周器を入れる方法があります。この方法では、入力周波数のN/M倍の出力周波数を得られます。その他に図4(d)のように、VCOから分周器の間に固定分周器を追加して、入力周波数のN×M倍の出力を得る方法もあります。この方法は、VCOの出力をGHzまで高めて、高周波出力を得るのに活用できます。

PLL回路では、設定分解能を上げると分周数を大きく取る必要があり、位相比較周波数が低くなります。分周設定を変更した場合のPLLの応答性の低下や、設定分解能の増加でループ利得低下が発生し、出力波形のジッタや位相雑音特性に影響を与えます。

Copyright © ITmedia, Inc. All Rights Reserved.