Tabulaが100Gbps通信機器向けの3次元PLDを投入、Intelの22nmプロセスで製造:プログラマブルロジック FPGA

TabulaのFPGA「ABAX2P1 3PLD(Programmable Logic Device)」は、100ギガビット/秒(Gbps)クラスの信号を扱う通信機器などに向けたFPGAである。チップ上の2次元平面に「時間」の次元を加えた、独自の3次元PLD技術を採用しており、Intelの22nmプロセスで製造される。

米国の新興FPGAベンダーであるTabula(タブラ)は2013年3月26日(米国時間)、100ギガビット/秒(Gbps)クラスの信号を扱う通信機器などに向けたFPGA「ABAX2P1 3PLD(Programmable Logic Device)」を発表した。このFPGAは、Intelが開発した3次元ゲート(Tri-Gate)構造のトランジスタ技術を用い、22nmプロセスで製造される。エンジニアリングサンプル品は2013年第3四半期(7〜9月)より供給される予定だ。同時に、設計開発ツール「Stylusコンパイラ リビジョン2.6」の利用も可能となる。

ネットワークのトラフィックが増大し、パケット処理を行う通信機器には高い処理能力が求められている。Tabulaのマーケティング担当でバイスプレジデントを務めるAlain Bismuth氏は、「データセンターなどで使われる通信インフラ装置では、データの転送速度が10〜40Gbpsから100Gbpsに対応したものへの移行が明確となっている。新製品はこのようなシステムにおいてパケット処理を高速に行う必要のある用途をターゲットにしたチップである」と話す。

ABAX2P1 3PLDは、同社がSpacetime(スペースタイム)と呼ぶ独自の動的再構成(ダイナミックリコンフィギュレーション)技術に基づくアーキテクチャを採用したFPGAである。外部から供給されるシステムクロックをFPGAの内部で逓倍(ていばい)して、高速クロックを生成する。そのクロックでプログラマブルロジック領域を駆動するとともに、回路の再構成も行う。現行製品は最大8逓倍(8回の書き換え)までだったが、ABAX2P1 3PLDは最大12逓倍まで可能としており、システムクロックの1サイクルで最大12回の再構成(書き換え)を実行できるという。

これによって、たとえプログラマブルロジック領域の物理的な規模が一定でも、時分割でより高速に回路を切り替えられれば、実効的なロジックの規模を増やせるという。Tabulaは、チップ上の2次元平面に「時間」の次元を加えて、実効的なロジック規模を増大させた3次元のFPGAを3PLDと呼んでいる。

さらにABAX2P1 3PLDは、論理回路やメモリ、MACブロック、インターコネクトなど、チップ内部に実装されるコンポーネントが全て最大2GHzで動作するIP(Intellectual Property)コアとなっている。オンチップのメモリは、容量が23.6Mバイトで、スループットは13.8テラバイト/秒、レイテンシは1.5nsとなっている。また、3PLDアーキテクチャにより、さらに短いインターコネクトを実現することで、タイミングクロージャに対する技術者の負荷を軽減させられるとみている。

ABAX2P1 3PLDは、Spacetimeや3PLDといった独自のアーキテクチャを採用したFPGAである。これらの独自アーキテクチャは、技術者が回路設計を行う際の手間を増やす可能性がある点が課題となる。しかし、設計開発ツールの「Stylusコンパイラ リビジョン2.6」を使えば、再構成の書き換え回数などこれらのアーキテクチャのことを意識しなくても、ABAX2P1 3PLDの期待値の性能を得られる。

Stylusコンパイラ リビジョン2.6は、「シーケンシャル・タイミング」という手法を用いることで、タイミングクロージャを短時間で行うことができる。また、後で行う配線を前もって考慮しながら配置設計を行う機能などを備えている。

もし、タイミングが設計通りに収束しない場合、問題となっている場所を明示するだけでなく、その理由もリポートされるため、改善しなければならないポイントがより明確となる。さらに、配線を意識した配置が行われるため、設計の早い段階でインターコネクトの遅延などをより正確に把握でき、設計作業の手戻りを少なくすることができる。この他にも、ユーザーは必要なレイテンシとスループットを事前に指定しておけば、チップの性能と集積度の優先順位を考慮しながら、ツール側で自動的に最適化してくれる、といった特長を備えている。

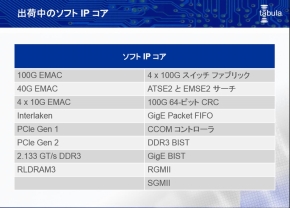

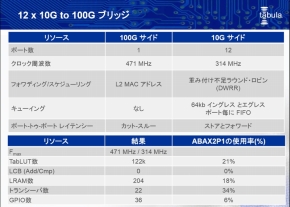

Tabulaは、ABAX2P1 3PLDに加えて、100G EMACやInterlakenなどのソフトウェアIPコア、RTLソースコードも出荷中である。また、12×10Gと100G間のブリッジ、4×100Gスイッチ、TSE(Ternary Search Engine)といったリファレンスデザインキットや設計事例などを用意した。リファレンスデザインキットは2013年第2四半期(4〜6月)より提供される。

出荷中のソフトウェアIPコア一覧表(左)。「ABAX2P1 3PLD」を用いた12×10Gと100G間のブリッジでは、クロック周波数471MHz/314MHzを達成した。しかも使用するLUT(ルックアップテーブル)数は12万2000で、リソース全体の21%しか必要としない(右側)。(クリックで拡大) 出典:Tabula

出荷中のソフトウェアIPコア一覧表(左)。「ABAX2P1 3PLD」を用いた12×10Gと100G間のブリッジでは、クロック周波数471MHz/314MHzを達成した。しかも使用するLUT(ルックアップテーブル)数は12万2000で、リソース全体の21%しか必要としない(右側)。(クリックで拡大) 出典:TabulaCopyright © ITmedia, Inc. All Rights Reserved.

関連記事

「3次元PLD」のTabulaが日本事務所を開設、日本市場の開拓に本腰

「3次元PLD」のTabulaが日本事務所を開設、日本市場の開拓に本腰

既に国内の代理店契約を結んでいる半導体技術商社のルネサスイーストンはデザインサービスや物流機能の提供に注力し、新たに開設した日本事務所がセールスとマーケティング、エンジニアリングの中心的な機能を受け持つ。 Intelがファウンダリ事業を加速、22nmで新興FPGAベンダー2社目を獲得

Intelがファウンダリ事業を加速、22nmで新興FPGAベンダー2社目を獲得

Intelは、FPGAの新興ベンダーであるTabulaの製品を、22nm世代の3次元構造のトライゲートトランジスタ技術を適用して製造する。この2社に関しては、2011年5月にファウンドリ契約を結んだという報道が流れており、このほどそれが公式に発表された形だ。 これまでの動的再構成チップとは違う、3次元PLDのTabula社長が来日会見

これまでの動的再構成チップとは違う、3次元PLDのTabula社長が来日会見

Tabulaは、プログラマブルロジック領域に実装する回路を動的に再構成し、時分割で書き換えることで実効的なロジック規模を拡張する「3PLD」を手掛ける新興ベンダーだ。動的再構成技術はこれまでさまざまな企業が提案したものの、一般的な普及には至っていない。3PLDはそうした過去のチップとは違うという。