想像以上に難しい14nmプロセス、設計面での課題が山積:プロセス技術

14nmプロセス技術を確立することは、設計者たちが予想していたよりも、はるかに難しいようだ。プロセスの微細化が進むに連れて、リーク電流の増加などの課題が浮き彫りになった。IBMのエンジニアは、「14nm世代では、これまでの対応策が通用しなくなる」との見解を述べている。

2013年3月24〜27日に米国ネバダ州で開催された「International Symposium on Physical Systems(ISPD)」で専門家に聞いたところ、14nmプロセス技術を確立することは、当初の想像よりもはるかに難しいようだ。ISPDは、毎年世界中から半導体設計者が集まるイベントである。

半導体の微細化は、チップの小型化と動作クロックの高速化を実現した。チップが小さくなるほど、クロック周波数は上がり、動作電圧は低下した。

だが、残念なことに、過去数世代のプロセス技術がもたらした、クロック周波数と動作電圧の変化はごくわずかなものであった。ゲート絶縁膜が非常に薄くなったことによるリーク電流の増加など、回路設計において課題や制約が出てくるようになったからだ。

IBMの著名なエンジニアであるJames Warnock氏の論文「Circuit and Physical-Design Challenges at the 14-nm Technology Node.(14nmノードにおける回路設計および物理設計の課題)」によると、これまでは、High-k(高誘電率)材料を用いて膜厚を確保するなど、多くの“応急処置”が施されてきたが、それは単に根本的な問題の対処を14nm世代まで先送りにしただけのことだったという。

Warnock氏は、「微細化に伴う課題の根本的な解決が先送りにされてきたためか、14nm世代では、それらの課題による影響が極めて大きくなっている。微細化の限界は近づいている。最終的には製造コストなど、経済的な問題も関わってくるが、14nm世代では、微細化そのものだけで性能を上げられないだろう」と述べた。

微細化の最大の課題はトランジスタのリーク電流の増加だ。これまでの世代では、サブスレッショルドスロープの傾きを急にして閾(しきい)値電圧を下げたり、High-k材料を用いて膜厚を確保したりして対応してきた。リソグラフィでは、EUV(極端紫外線)技術確立の遅れをダブルパターニングによって補ってきた。だが、いずれの策も14nm世代では通用しないとWarnock氏はいう。

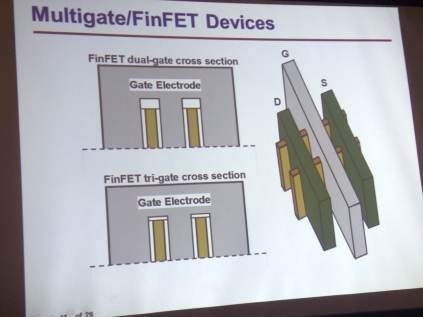

Warnock氏は、「リーク電流の問題を解決する手段の1つとして、Intelが22nmプロセスで用いた3次元のFinFETがある。FinFETは、すぐに他のチップメーカーも採用し始めた。FinFETのサブスレッショルドスロープは急峻(きゅうしゅん)であり、ばらつきの1種であるRDF(Random Dopant Fluctuation)を改善する。一方でFinFETは、フィン(ひれ)の幅や高さといった、新たなばらつき要因ももたらす」と述べた。

【翻訳:青山麻由子、編集:EE Times Japan】

関連キーワード

14nmプロセス | FinFET | 設計 | 半導体 | プロセス技術(エレクトロニクス) | IBM | リソグラフィ | EUV(極端紫外線) | Intel | high-kメタルゲート | 半導体設計(EDA)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解

「Common Platform Technology Forum」において、IBMが半導体製造技術の将来展望について発表を行った。液浸リソグラフィによるダブルパターニング技術やFD-SOI技術に加え、カーボンナノチューブ、シリコンフォトニクス、ナノワイヤーなどのキーワードを交えて半導体製造の将来像や課題などが示された。 Intel、14nmプロセスの導入を延期か

Intel、14nmプロセスの導入を延期か

Intelの14nmプロセスの導入が遅れる可能性が出てきた。14nmチップを製造するためのトレーニングを米国で受けていたアイルランド工場に所属する600人の従業員が、予定よりも早く帰国している。一方、ファウンドリ専業のGLOBALFOUNDRIESは、14nmプロセスについて強気のロードマップを発表している。 EUVは本当に実用化できるのか?

EUVは本当に実用化できるのか?

半導体製造技術のロードマップでは、193nmリソグラフィに限界が来たら、157nmフォトリソグラフィへと移行するはずだった。しかし、実際に普及したのは193nmの液浸リソグラフィであった。次の技術として名前が挙がるのはEUVだが、「この技術が実際に商業用途で利用されるかどうかは定かではない」と指摘する声がある。