動作電圧0.4V以下を実現する技術を開発、スマホの消費電力も1/10になる!?:プロセス技術(1/2 ページ)

新エネルギー・産業技術総合開発機構(NEDO)と超低電圧デバイス技術研究組合(LEAP)は、動作電圧が0.4V以下のロジックLSIやメモリを実現できる技術を開発した。これらの技術を使ったLSIを搭載した機器は、消費電力を1/10に低減できる可能性がある。

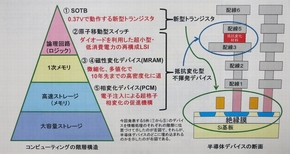

新エネルギー・産業技術総合開発機構(NEDO)と超低電圧デバイス技術研究組合(LEAP)は2013年6月10日、動作電圧が0.4V以下のロジックLSIやメモリを実現できる技術を開発したと発表した。大きく分けて、動作電圧が0.37Vと小さいSOTB(Silicon on Thin BOX)を用いた「新型トランジスタ」技術と、磁性変化デバイス(MRAM)や相変化デバイス(PCM)などで、大容量や低消費電力を実現するための「抵抗変化型不揮発デバイス」技術である。これらの技術を使ったLSIを搭載したIT機器は、消費電力を1/10に低減できる可能性があるという。

今回の研究成果は、6月11〜14日に京都で開催される半導体デバイスとプロセス技術に関する国際学会「2013 Symposium on VLSI Technology」において、LEAPから詳細が発表される。

ICチップはこれまで、微細化技術の進展によって性能の向上と消費電力の低減などを実現してきた。チップの動作電圧を下げていくと消費電力削減の効果は大きいが、微細化に伴うトランジスタの特性ばらつきやリーク電流が増大する。このため、動作電圧が1V以下になると微細化技術だけで消費電力を削減することは難しくなっていた。そこで今回は、トランジスタ構造や記憶のメカニズムを変えることで、「動作電圧が1V以下」という低電圧動作の壁を乗り越えていく技術を開発した。これによって、電池1本で長期間動作できる機器や、環境発電を活用した電池レス機器などへの応用が可能となる。

今回LEAPが発表する論文は5件ある。そのテーマは、(1)薄膜BOX-SOI(SOTB)を用いた2MビットSRAMの超低電圧0.37V動作を実証、(2)金属原子移動型スイッチを用いた再構成可能LSIの超小型化に道筋、(3)CPUに混載するキャッシュメモリ向けに、微細化による高密度化を実現できるスピン注入型MRAMを開発、(4)CPUに混載するキャッシュメモリ向けに、高密度化を実現できる4値/セルのスピン注入型MRAMを開発、(5)データセンター向けSSDの適用を目指した相変化デバイスの低消費電力動作に成功、である。(1)が新型トランジスタに関するテーマで、(2)〜(5)は抵抗変化型不揮発性デバイスに関する開発成果である。

Copyright © ITmedia, Inc. All Rights Reserved.