DRAM各社のプロセスを比較、さらなる微細化は可能か:メモリ/ストレージ技術(2/2 ページ)

DRAMは、幾度となく「微細化はもう限界」だと言われてきた。だが、メーカー各社は2Xnmや1Xnm世代のDRAMの実現に向けて試行錯誤を繰り返し、成果を出し始めているという。

ストレージキャパシタの微細化

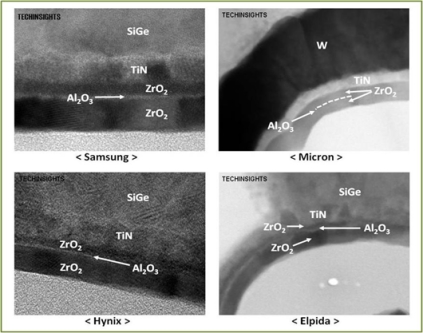

ストレージキャパシタでは、3Xnm世代のセルの鍵になるのは、ZrO2の間に挟み込む、非常に薄いAl2O3の層だ。4社とも同様のマルチレイヤースタックを採用している。このマルチレイヤースタックは、ZAZ TITと呼ばれるもので、TiN/ZrO2/Al2O3/ZrO2/TiNの層から成る*1)。

*1)TiN(窒化チタン)、ZrO2(酸化亜鉛)、Al2O3(酸化アルミニウム)

薄膜のAl2O3層は、リーク電流を抑えるために、ZrO2の間に挟まれている。

3次元のシリンダ型キャパシタの絶縁体の厚さは、さらなる微細化におけるもう1つの課題だ。3XnmのDRAMセルの多くは、厚さ7〜9nmのマルチレイヤー絶縁体を用いている。将来的に1XnmクラスまでDRAMのセルアーキテクチャを微細化するには、これよりもさらに薄くすることが必須となるだろう。

Micron/Nanya以外のメーカーは、TiNプレートの上にSiGe(シリコンゲルマニウム)層がある。Micron/Nanyaは、SiGeではなくタングステン(W)層を形成している。SK-Hynixは、二重層にしたポリSiプラグをドレイン領域のストレージノードに接続している。一方のエルピーダは、二重層のタングステン/TiNとポリSiプラグを用いている。

埋め込みワード線を採用したSDRAMの多くは、アレイ領域にトリプルウェルを用いている。トリプルウェルとは、p型基板上に設けたNウェルの上に、Pウェルを形成したものである。

しかし、Micron/Nanyaの31nm SDRAMセルアレイは、4重のウェル(quadruple well)の構造を持つ。これは、n型基板にドープしたPウェルの上にNウェルを、さらにその上に浅いPウェルを形成したものだ。

PCに加え、スマートフォンやタブレット端末といったPC以外の機器での需要が高まっていることから、DRAMセルのさらなる微細化が求められている。最新のプロセス技術やリソグラフィ技術の進歩のおかげで、DRAMセルアレイは、30nm、20nmクラスまで微細化される可能性がある。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ

スピン注入式の新型MRAMがいよいよ製品化、2015年にはギガビット品が登場へ

DRAMに近い高速性と書き換え耐性が得られる次世代不揮発メモリとして注目されるMRAM。これまでに製品化されていたトグル方式のMRAMは記憶容量に制約がありDRAMを置き換える応用は難しかった。この状況が変わる。大容量化の有力手段として期待がかかるスピン注入方式を使った、新型MRAMの製品化が始まった。 Samsung、1Xnm世代の128GビットNANDフラッシュ量産へ

Samsung、1Xnm世代の128GビットNANDフラッシュ量産へ

Samsung Electronicsが、1Xnm世代のNAND型フラッシュメモリの量産を開始すると発表した。だが、Samsungは同製品について、読み出し/書き込み性能や、書き換え耐性などを一切明らかにしていない。 12個の原子で磁気メモリを構成、HDDの記録密度が100倍に高まる可能性も

12個の原子で磁気メモリを構成、HDDの記録密度が100倍に高まる可能性も

わずか12個の磁性原子に1ビットの情報を記録する技術を、IBMの研究グループが開発した。現在のハードディスク装置や半導体メモリチップに比べて、100倍以上もの高い記憶密度を実現できるという。