DDCトランジスタとフラッシュメモリの混載技術、富士通セミコンが開発:IEDM 2013

富士通セミコンダクターは、DDC(Deeply Depleted Channel)技術を適用したロジック回路とフラッシュメモリセルを同一チップに混載し、同社三重工場の55nmプロセスで製造できる技術を開発したと発表した。これまで高温でのプロセス処理が必要とされてきたフラッシュメモリセルを、低温プロセスのみで形成することに成功したことで、ロジック回路との混載を可能とした。

富士通セミコンダクターは2013年12月、DDC(Deeply Depleted Channel)技術を適用したロジック回路とフラッシュメモリセルを同一チップに混載し、同社三重工場の55nmプロセスで製造できる技術を開発したと発表した。これまで高温でのプロセス処理が必要とされてきたフラッシュメモリセルを、低温プロセスのみで形成することに成功したことで、ロジック回路との混載を可能とした。開発成果はIEDM(International Electronic Device Meeting)2013(2013年12月9〜11日、米国ワシントンDC)において発表した。

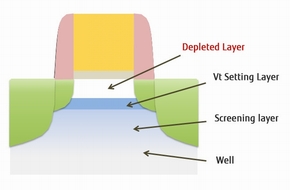

DDC技術は、SuVoltaよりライセンスを受けて共同開発した低消費電力化技術である。この技術を使ったDDCトランジスタは、ゲート電極の直下に、不純物を極低濃度に保った「Depleted Layer」と呼ばれる層を形成する必要がある。この層を保持するために、ウエハーを加工するこれ以外の工程においても、高温で処理するプロセスを用いることができなかった。

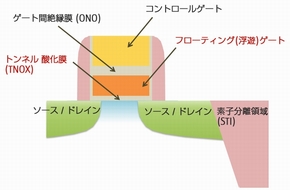

一方、FLOTOX(Floating Gate Tunnel Oxide)構造のフラッシュメモリセルでは、浮遊ゲートに注入された電子が漏れる「シングルビットチャージロス(SBCL)」を防止するため、トンネル酸化膜の形成工程などで最大1000℃の高温処理が必須となっていた。このため、DDCトランジスタとFLOTOX構造のフラッシュメモリセルを同一チップに混載して、実用的な特性を達成するのは製造上、困難とみられていた。

今回の開発で同社は、低温プロセスのみでFLOTOX構造のフラッシュメモリセルを形成する方法を見出した。試作した評価用チップでは、DDCトランジスタに要求される特性を維持しつつ、フラッシュメモリセルでもSBCLによる不良が発生しないことを確認した。

その上、SBCLの発生メカニズムとして新たな知見が得られたという。これまでは、トンネル酸化膜への電流ストレスによってSBCLが生じるとみられてきた。ところが今回の研究で、SBCLはドレイン近傍で発生するホットホールによって支配されていることが明らかになった。

同社は、「一例だが、あらゆる機器がインターネットにつながる『IoT(Internet of Things)』に対応するセンサーネットワーク向けLSIなどに、不揮発性メモリの搭載が求められている」として、今回開発した技術をこれらの用途向けLSIに応用していく考えだ。なお、実用化時期については未定である。

関連キーワード

富士通 | フラッシュメモリ | 富士通セミコンダクター | トランジスタ | Internet of Things | LSI | センサーネットワーク | インターネット | ネットワーク | 不揮発性メモリ

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

富士通セミコンが最終レイアウト工程を最短1カ月で完了させる新設計手法を開発

富士通セミコンが最終レイアウト工程を最短1カ月で完了させる新設計手法を開発

富士通セミコンダクターは、28nmプロセスなど先端プロセスを用いるカスタムSoC(System on Chip)開発向けに、高密度集積と開発最終段階のレイアウト工程を最短1カ月で完了できる新設計手法を開発したと発表した。 インテル、富士通の携帯電話機用RFIC事業を買収

インテル、富士通の携帯電話機用RFIC事業を買収

Intel(インテル)が2013年7月に、富士通セミコンダクター(以下、富士通セミコン)の携帯電話機向けRFトランシーバIC(RFIC)事業を買収していたことが明らかになった。 富士通、GaNパワーデバイス事業をTransphormと統合

富士通、GaNパワーデバイス事業をTransphormと統合

富士通とその子会社富士通セミコンダクター(FSL)は2013年11月28日、Transphorm(トランスフォーム)と窒化ガリウム(GaN)パワーデバイス事業を統合すると発表した。