ムーアの法則、28nmが“最後のノード”となる可能性も:ビジネスニュース オピニオン(2/2 ページ)

ムーアの法則というのは、そもそも「部品コストを最小限に抑えるための複雑さ」を示すものだ。その観点で考えると、実質的には28nmが“最後のノード”になる可能性がある。

SRAMセルのスケーリングも重要に

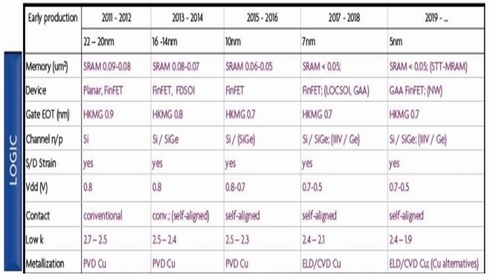

ただし、SoCの面積は、トランジスタ密度よりもSRAMセルのサイズに依存するところが大きい(関連記事:微細化に堪え得るオンチップSRAM)。そして、SRAMセルのスケーリングは、28nm以降は大幅に低下するのだ。28nmでは、ビットセルのサイズは約0.12μm2である。下の図は、ベルギーIMECが、2013年10月の「ロジック/メモリ製品ロードマップのアップデート」で発表したものだ。

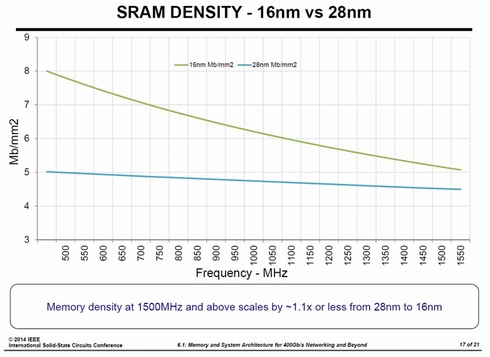

28nm以降では、SRAMのビットスケーリングの比率は、ノード当たり約20%になる。28nmまでは50%が一般的だった。だが、下記の図にある通り、実際の比率はさらに低い。この図は、Cypress Semiconductors メモリ製品部門のCTOを務めるDinech Maheshwari氏が、「ISSCC 2014」の招待論文で示したものだ。

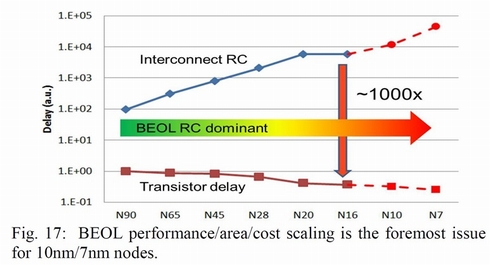

さらに、下図で示す通り、配線工程(BEOL)のRC遅延も微細化に伴って増すばかりだ。この図は、Qualcommの技術部門でバイスプレジデントと務めるGeoffrey Yeap氏が、「IEDM 2013」の論文で掲載したものである。

これらをまとめると、多くのSoCにとって、28nmが“コストを最小限に抑える”ノードになるということが分かる。現在、半導体業界は、「微細化=低コスト化ではない」というパラダイムシフトに直面している。これを考慮すれば、IEEEが、SOI(Silicon On Insulator)のカンファレンスを拡張し、「IEEE S3S(SOI technology, 3D Integration, and Subthreshold Microelectronics)」に名称を改めたことにも納得がいく。

IEEE S3S 2014は、10月6〜9日に米国サンフランシスコで開催される予定だ。これまで主流技術ではなかったSOIや3次元積層技術について、多くの情報を得られるよい機会となるだろう。

【翻訳:滝本麻貴、編集:EE Times Japan】

関連キーワード

28nmプロセス | ムーアの法則 | SOI | トランジスタ | CMOS | ビジネスニュース(EE Times Japan) | オピニオン(エレクトロニクス) | プロセス技術(エレクトロニクス)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ST、28nm FD-SOIチップの生産準備を完了

ST、28nm FD-SOIチップの生産準備を完了

STは、28nmプロセスを適用したFD-SOIの試作品を生産する準備が整ったと発表した。同社は、「FD-SOIは、プレーナ型バルクCMOSやFinFET CMOSなどに比べて、性能や消費電力、製造性の間のトレードオフが少ない」と主張している。 ムーアの法則が終えんを迎えればメリットになる――ブロードコムCTOインタビュー

ムーアの法則が終えんを迎えればメリットになる――ブロードコムCTOインタビュー

Broadcom(ブロードコム)のCTO兼会長であるHenry Samueli氏は、「微細化の限界は5nmから7nmプロセスになるだろう」と予想する一方で、28nmプロセス以降では、コストがあまりにも高いため、「微細化の魅力は薄れつつある」と述べる。 「ムーアの法則は今後10年以上は続く」、Intelが“限界説”を否定

「ムーアの法則は今後10年以上は続く」、Intelが“限界説”を否定

“ムーアの法則の終えん”がささやかれて久しいが、IntelのシニアフェローであるMark Bohr氏は、「CMOSのスケーリング(微細化)は少なくとも10年以上は続く」と分析している。