高性能デジタル編:PCとモバイルを牽引する最先端プロセッサ:徹底プレビュー「ISSCC2015の歩き方」(9)(1/2 ページ)

ISSCC最大の注目分野。それが「高性能デジタル」である。それだけに注目すべき発表は多い。今回は、IBMやOracleのサーバ向けの大規模プロセッサや、シリコンダイに固有な信号であるPUFを使ったセキュリティ向けの技術といった講演を紹介したい。

ISSCC最大の注目分野「高性能デジタル」

「高性能デジタル」はISSCCを構成するさまざまな半導体チップの中で、最も関心が集まるテーマと言える。サーバや高性能PC、スマートフォンなどの最新製品が搭載するマイクロプロセッサやSoC(System on a Chip)などの回路技術が発表されるからだ。

「高性能デジタル」に関連するセッションは3つ。セッション4とセッション14、セッション23である。セッション4のサブテーマは「プロセッサ」で、2015年2月23日月曜日午後1時30分に始まる予定となっている。ここではサーバ向けやハイエンドPC向けの最先端マイクロプロセッサが発表される。セッション14のサブテーマは「デジタルPLLとSoCビルディングブロック」で、2月24日火曜日午後1時30分に始まる予定となっている。ここでは高性能デジタルチップに不可欠な要素技術が披露される。セッション23のサブテーマは「低消費電力SoC」で、2月25日水曜日午後1時30分の開始予定である。ここではモバイル向けのアプリケーション・プロセッサが登場する。

本稿では少し順序を変え、セッション4、セッション23、セッション14の順に注目講演をご紹介しよう。

IBMのSystem zプロセッサとOracleのSPARCプロセッサ

セッション4(サブテーマは「プロセッサ」)は、サーバ向けを中心とする高性能大規模プロセッサの講演セッションであり、注目すべき発表が少なくない。

セッションの最初は、米国とドイツ、インドと世界各地のIBMによる共同開発として、ハイエンドサーバー「IBM System z」シリーズ向けのマイクロプロセッサが発表される(講演番号4.1)。22nmのSOI CMOS技術と17層金属配線技術を駆使しており、5GHzと高い周波数で動く。内蔵するCPUコアは8個。デュアルスレッディング処理に対応しているので、全体では最大16個のスレッドを並行して処理できる。2次キャッシュと3次キャッシュに埋め込みDRAM(eDRAM)技術を採用しており、それぞれ4Mバイト、64Mバイトの記憶容量を有する。

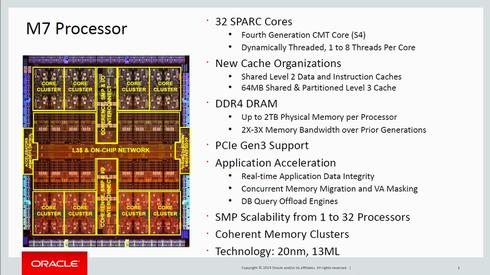

続いて米国のOracleが、SPARCアーキテクチャの次世代プロセッサ「SPARC M7」を発表する(講演番号4.2および講演番号4.3)。内蔵するCPUコアの数は32個と多い。4個のCPUコアで構成される1個のCPUクラスタが、2次キャッシュと3次キャッシュを共有する。CPUクラスタ当たりのキャッシュ容量は2次命令キャッシュが256Kバイト、2次データキャッシュが512Kバイト(256Kバイトを2個のCPUコアが共有×2ユニット)、3次キャッシュが8Mバイトである。製造技術は20nm、13層金属配線技術。

Oracleが2件の講演を終えた後は、スイスIBM Researchと米国Freescale Semiconductorの共同開発成果が発表される(講演番号4.4)。マイクロサーバ向けの64ビットSoCである。28nm CMOS技術で製造し、1.8GHzで動作した。12個のCPUコアを内蔵する。

このセッションの最後には、米国AMDがx86互換のCPUとGPUを統合したプロセッサ(APU:Accelerated Processing Unit)を発表する(講演番号4.8)。内容は、次世代のPC向けAPU「Carrizo(カリーゾ)」の技術概要だとみられる。Carrizoは28nmのバルクCMOSプロセスで製造されている。トランジスタ数は24億1000万個に達する。シリコンダイ面積は245mm2。

Copyright © ITmedia, Inc. All Rights Reserved.