メモリ編:次世代大容量フラッシュと次世代高速DRAMに注目:徹底プレビュー「ISSCC2015の歩き方」(11)(2/3 ページ)

今回は、大容量化と高速化が進む半導体メモリに焦点を当てる。メモリ市場の二大勢力となっているDRAMとNANDフラッシュメモリについての講演が多い。15nmプロセスを採用したNANDフラッシュメモリや、車載マイコン向けフラッシュメモリ技術、次世代のDRAMインタフェースなどに関する発表がある。

128Gビットの超高密度NANDフラッシュメモリ

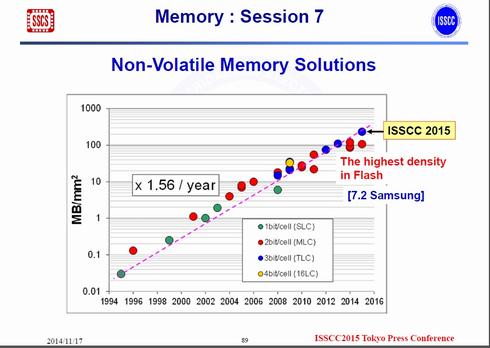

過去のISSCCを見ていくと、NANDフラッシュメモリの記憶密度(シリコン面積当たりの記憶容量)は20年ほどの期間、1年に1.56倍の割合で増加してきた。これは15年ほどで記憶密度がおよそ1000倍に達するという、物凄い拡大ペースである。恐るべきことにISSCC2015でも、このトレンドは維持された。平方ミリ当たりに200Mバイト(1.6Gビット)という記録密度のシリコンメモリチップが登場する。

ISSCCで発表された不揮発性メモリ(実際にはNANDフラッシュメモリ)の記憶密度の推移。ISSCC2015では、200Mバイト(1.6Gビット)/mm2を初めて超える。2014年11月17日に開催された「ISSCC2015東京記者会見」の説明資料から引用した(クリックで拡大)

その超高密度NANDフラッシュメモリを含む、不揮発性メモリに関するセッションがセッション7(不揮発性メモリソリューション)である。このセッションでは、東芝グループと韓国のSamsung Electronicsがそれぞれ、NANDフラッシュメモリの大容量化技術を発表する。

東芝と米国のSanDiskは、15nmと極めて微細な加工技術による64GビットのMLC方式NANDフラッシュメモリを共同で報告する(講演番号7.1)。電源電圧は1.8V。記憶密度はおよそ100Mバイト/平方ミリで、従来技術の延長であるプレーナ型メモリセルのNANDフラッシュとしては、最も高い密度を達成した。

韓国のSamsung Electronicsは3次元メモリセル技術による128GビットのTLC方式NANDフラッシュメモリを発表する(講演番号7.2)。3次元積層するメモリセルの層数は32層と多い。記憶密度は半導体メモリとしては過去最高の、約200Mバイト/平方ミリに達する。

この他、ルネサス エレクトロニクスが、170℃と高温で動作する車載マイコン用フラッシュメモリ技術を発表する(講演番号7.3)。読み出し周波数は200MHzと高い。製造技術は28nmである。

またこのセッションでは、東芝がオンチップキャッシュに向けた磁気メモリ(STT-MRAM)技術の開発成果を報告する(講演番号7.5)。アクセス時間は3.3nsと短い。動作周波数当たりの消費電力は71.2μW/MHzとかなり低い。1Mビットのテストチップを試作してみせた。

Copyright © ITmedia, Inc. All Rights Reserved.