ARMから見た7nm CMOS時代のCPU設計(7)〜CPUコアの性能をレイアウトが大きく左右:福田昭のデバイス通信(18)(1/2 ページ)

今回は、CPUコアの性能(動作周波数)とレイアウト設計の関係を見ていこう。CPUコアの性能は、レイアウト設計によって大きく変わる。CPUコアの性能とシリコン面積、消費電力は独立ではない。回路が同じでも、シリコン面積が2倍違うということもある。逆に、回路を工夫すれば、トランジスタ数を減らしてシリコン面積を削減することも可能だ。

CPUコアの性能はレイアウト設計で大きく変化

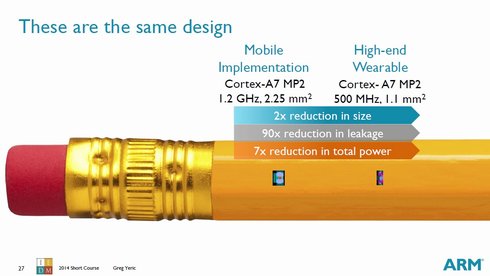

前回は、同じ回路図でもシリコンの物理的なマスクレイアウトにはさまざまなバリエーションがあることを説明した。ARMのCPUコア製品では、同じアーキテクチャ、同じ回路図のCPUコアでも、性能がまったく異なるシリコン(物理IP)を提供している。講演では「ARM Cortex-A7 MP2」(A7のデュアルコア品)の例を示していた。

ここでは2通りの物理IP(シリコン)を見せていた。1つはモバイル機器向けのA7コアである。最大動作周波数は1.2GHzとかなり高い。シリコン面積は2.25mm2である。もう1つはハイエンドのウェアラブル機器向けに、消費電力を大幅に低減したA7コアである。回路そのものは同じであるにもかかわらず、シリコン面積は1.1mm2と約半分に小さくなっている。消費電力は1/7、リーク電流は1/90と大幅に低減できた。最大動作周波数は500MHzに下がっている。

動作周波数とシリコン面積の関係

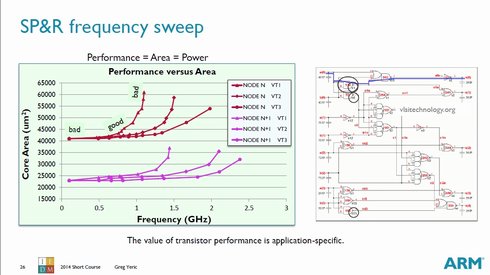

CPUコアの性能(動作周波数)とシリコン面積、消費電力は独立ではない。お互いに影響しあう。動作周波数を上げようとすると普通はシリコン面積が拡大し、消費電力が増加する。動作周波数とシリコン面積の関係だけを考えたときは、トランジスタのしきい電圧(VT)が動作周波数の上限を決める。

最大動作周波数が低い領域では、CPUコアのシリコン面積はほぼ一定であり、また、しきい電圧の違いによるシリコン面積の違いはほとんどない。最大動作周波数を上げていくと、あるところから、シリコン面積が増大する。シリコン面積の増加が始まる周波数は、しきい電圧によって異なる。しきい電圧が低いトランジスタで設計したCPUコアは、シリコン面積が小さく、動作周波数が高い。

Copyright © ITmedia, Inc. All Rights Reserved.