ARMから見た7nm CMOS時代のCPU設計(18)〜壁に突き当たるリソグラフィ技術:福田昭のデバイス通信(29)(2/2 ページ)

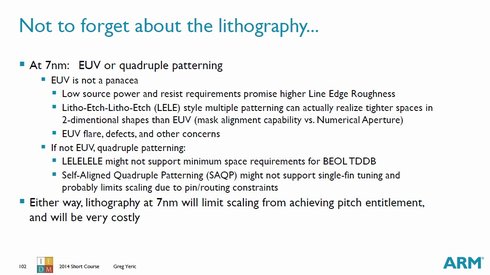

プロセスルールの微細化において最も困難な課題は、リソグラフィ技術にある。7nm世代の半導体を量産するためのリソグラフィ技術は、いまだに確定していない。現在のところ、解決策としては、従来のArF液浸リソグラフィ技術の改善か、EUV(極端紫外光)リソグラフィ技術の開発が挙げられている。

インフラから作り変えるEUVリソグラフィ

7nm時代を実現する、もう1つの手法は、まったく新しいリソグラフィ技術の開発である。きわめて短い波長の光を光源とすることで、解像度を飛躍的に高める。研究開発が進んでいるのは、波長が13.5nmと短い極端紫外光(EUV:Extreme Ultra Violet)を光源とするリソグラフィ技術である。「EUVリソグラフィ」と呼ばれることが多い。

波長(λ)が13.5nmでkファクタを0.35とすると、7nmを解像するために必要なNAは、0.67になる。従来のArFリソグラフィの常識では、非常に低いNAの光学系に見える。

ただしEUVリソグラフィでは、リソグラフィ技術を構成する数多くの要素技術、つまり、インフラストラクチャに相当する部分をほとんどゼロから構築しなければならない。例えば光学系である。従来のArFリソグラフィではレンズを主体とする屈折光学系を採用していた。光の透過損失がきわめて少ないレンズと強力なレーザー光源の組み合わせによって高いスループットを実現していた。しかしEUVリソグラフィの軟X線領域では屈折レンズの候補となる材料が今のところ、存在しない。このため、多層膜による反射鏡を組み合わせた反射光学系で光源からシリコンウエハーまで、光を導くことになる。

EUVリソグラフィ向けに開発された反射鏡の反射率は、それほど高くない。70%前後である。これは2枚の反射鏡を通しただけで、光の強度が半分になってしまうことを意味する。さらに、マスクが透過タイプではなく、反射タイプであることも、光エネルギーの利用効率を悪化させる。

こういった多大な光損失のしわ寄せを引き受けなければならないのが、EUV光源である。量産開始に必要なスループット(ウエハーの処理枚数)は1時間当たりに125枚とされている。このスループットを達成するには、光源の出力(厳密には「中間集光点」の出力)を250Wに高める必要がある。

EUV光源の開発には既に15年もの歳月と多大な努力が費やされてきた。最近までは光源の出力が100W未満で停滞しており、EUVリソグラフィの将来に関する見方は非常に厳しいものが多かった。ところが今年(2015年)の2月に米国シリコンバレーで開催された国際会議で、140Wの出力を達成した光源の開発発表と、1日に1000枚を超えるウエハーを処理した(平均光源出力換算で90Wを超える)との実験結果発表がなされた。さらに光源の出力が順調に上がるかどうかは未知数なものの、EUVリソグラフィの将来に明るい兆しが出てきたことは間違いない。

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ASMLがEUV装置を15台受注、納品先はIntel?

ASMLがEUV装置を15台受注、納品先はIntel?

ASMLが、EUV(極端紫外線)リソグラフィ装置を15台、“米国顧客企業の1社”に納入すると発表し、業界の観測筋の間でさまざまな臆測を呼んでいる。複数の情報筋が、この顧客企業がIntelではないかという見方を示している。 EUVは本当に実用化できるのか?

EUVは本当に実用化できるのか?

半導体製造技術のロードマップでは、193nmリソグラフィに限界が来たら、157nmフォトリソグラフィへと移行するはずだった。しかし、実際に普及したのは193nmの液浸リソグラフィであった。次の技術として名前が挙がるのはEUVだが、「この技術が実際に商業用途で利用されるかどうかは定かではない」と指摘する声がある。 ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

TSMCが、ASMLにEUV(極端紫外線)露光装置2台を発注していたことが明らかになった。TSMCは、EUVリソグラフィによって7nmプロセスの実現を目指すとみられている。2015年末には7nmプロセスを適用したチップのリスク生産が開始される可能性がある。 TSMC、10nmプロセスではインテルとの技術差なくなる

TSMC、10nmプロセスではインテルとの技術差なくなる

TSMCは、10nmプロセスを適用したチップの製造を2017年に開始する。同社は「インテルの10nmチップと同等レベルの性能を実現できると見ている。10nmプロセスで、インテルとの技術的なギャップを埋められるだろう」と述べている。