プレーナ型NANDフラッシュの微細化の限界:メモリ各社の製品から探る(3/4 ページ)

最近になって、1Xnm世代のプロセスを適用したプレーナ(平面)型のNAND型フラッシュメモリが市場に投入され始めた。だが、プレーナ型NANDフラッシュの微細化は限界だといわれている。各社の1Xnm世代NANDフラッシュを見ながら、微細化技術について考察してみたい。

Micronの16nm NANDフラッシュ

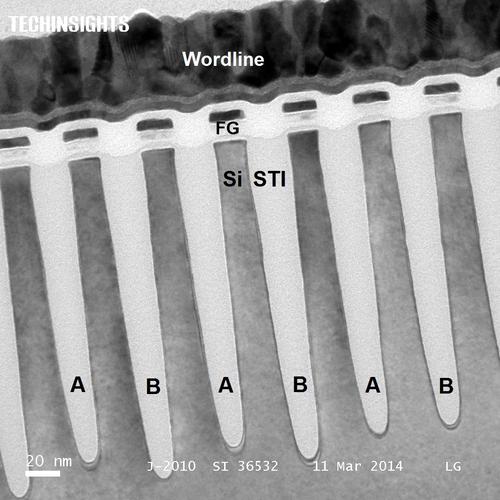

ダブルパターニングプロセスでは、サイドウォールスペーサの間隔が均一でない場合もある。これは、ABパターニングと呼ばれ、Micronの16nm NANDフラッシュ(図3)のSTI(Shallow Trench Isolation)パターニングで確認できる。

図3では、シリコンチャネルに整合させたプレーナ型フローティングゲート(浮遊ゲート)上で、左から右にタングステンのワード線が走っている。フローティングゲートとシリコンチャネルは、SADPによって、パターニングとエッチング処理が行われている。隣接するシリコンチャネル間のSTIの下部を見ると、特徴的なABパターニングがエッチングの深さに表れていて、SADPが適用されていることが分かる。

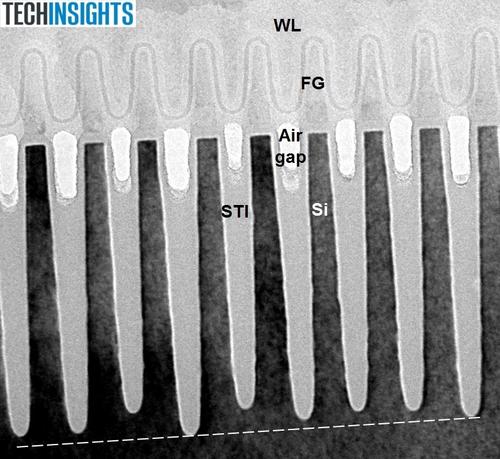

SK-Hynixは、同社の「Middle-1X(M1X)」nm世代のフローティングゲートNANDに、クアッドスペーサパターニングを適用している。同社は、「IEDM 2013」で発表したこの技術を、図4の16nm NANDフラッシュに適用していると思われる。

ただし、トレンチ下部のABパターンは、よりランダムなパターニングになっている。Samsungの16nm NANDフラッシュや東芝の15nm NANDフラッシュにも、これと同様のランダムなパターニングが見られることから、両社がクアッドスペーサパターニングプロセスを適用していると考えられる。

Copyright © ITmedia, Inc. All Rights Reserved.