CMOSプロセスでInGaAs FinFETを形成、Si/SOI基板上に:プロセス技術

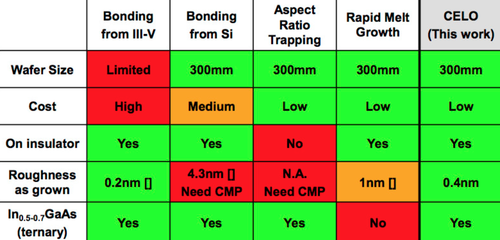

IBMがIII-V族化合物半導体を使ったFinFETの開発成果を積極的に発表している。IBMは、局所横方向エピタキシャル成長(CELO)技術により、シリコンおよびSOI基板の両方に、通常のCMOSプロセスで、InGaAsのFinFETを形成したと発表した。

IntelやSamsung Electronicsなどは現在、Si(シリコン)基板を使いながら、電子移動度がより高いIII-V族化合物半導体を利用する手法の開発に取り組んでいる。IBMは、標準的なCMOSプロセスでこれを実現する手法を発表した。

IBMは、SOI(シリコン・オン・インシュレータ)ウエハー上にIII-V族化合物半導体であるInGaAs(インジウムガリウムヒ素)を積層する技術を既に発表している*)。同社の別の研究チームがさらに優れた手法を発見したという。今回発表された手法は、通常のバルクシリコンウエハーを使用して、InGaAs FinFETを形成するというものだ。2015年6月15〜19日に京都で開催した国際会議「IEEE Symposium on VLSI Circuits」で報告した。

*)関連記事:「ムーアの法則」継続の鍵となるか、Si/III-V族の“ハイブリッド”ナノワイヤ

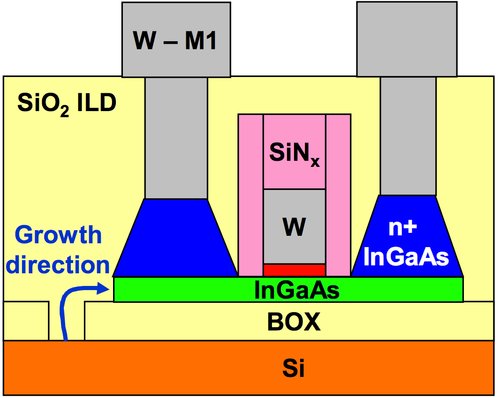

IBMの最先端機能材料部門でマネジャーを務めるJean Fompeyrine氏は、EE Timesに対して、「まずはSOI基板ではなく、バルクシリコンウエハーを使った。バルクシリコン上に酸化物層を形成したあと、シリコン基板に向けてトレンチを作る。そのトレンチを使ってシード層からInGaAsを成長させる。これは、非常に製造しやすいプロセスだ」と説明した。Fompeyrine氏は、この手法をIBM Researchの最先端CMOSサイエンティストであるLukas Czornomaz氏と共同で開発したという。

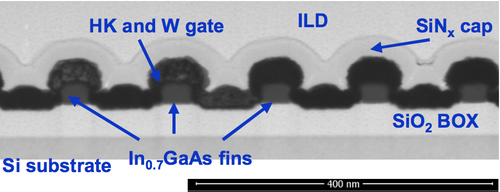

InGaAsは、シード層から成長し、ウエハーに対して水平方向に伸びていく。その後、端の部分がエッチングされて、InGaAsのトランジスタチャネル(緑色)が、Si基板上の埋め込み酸化膜(BOX)の上に形成される。メタルソース、ドレイン、そして、SiO2のILD(InterLayer Dielectric:層間絶縁膜、黄色)に覆われた高誘電体(赤)ゲート(灰色)も、ともに形成される 出典:IBM

IBMの手法は、ベルギーのIMECが開発した方法と似ている。ただしIBMは、IMECとは異なる新たな技術を導入している。IMECの手法では、InGaAsは垂直方向にのみ成長する。IBMの手法も最初は垂直方向に成長するが、その後、水平に内側に向かうように誘導する。垂直方向の成長パターンでは、結晶格子の不整合による欠陥が発生する場合があるが、同手法では、これが発生しないという。

Fompeyrine氏は、「この技術は、局所横方向エピタキシャル成長(CELO:Confined Epitaxial Lateral Overgrowth)と呼ばれるものだ。CELOは、欠陥の発生率を非常に低く抑えながら、InGaAsをエピタキシャル成長させるので、最先端のCMOSで必要とされるUTB(Ultra Thin Body)あるいはFin構造のトランジスタを形成できる」と説明している。CELOは、InGaAsの欠陥が非常に少ないため、III-V族化合物半導体を使ったプレーナ型とFin型の両方を、埋め込み酸化膜(BOX)上に形成できるとしている。

CELOによる、ゲートファースト方式で、自己整合構造のFinFET*)は、最先端のシリコン基板上のInGaAs MOSFETと同等レベルの電気特性を示すという。

*)サイズは、ゲート長が100nm、Fin幅は50nm、コンタクトプラグ間隔は250nm、厚さは30nm。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

微細化の限界に挑む、Siと新材料の融合で新たな展望も

微細化の限界に挑む、Siと新材料の融合で新たな展望も

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000 年代に入り、状況が変わってきた。 動き出すSiCパワー半導体、省エネルギーの切り札へ

動き出すSiCパワー半導体、省エネルギーの切り札へ

CO2の25%削減目標やこれまでにない規模の太陽光発電の導入、米国や中国を中心に急速に立ち上がり始めたスマートグリッドなど、従来とは異なる省エネルギー対策が必要となってきた。いずれも電力の変換技術が必要不可欠だ。ところが、電力変換用に用いられてきたSi(シリコン)パワー半導体の性能はこれ以上伸びそうにない。このような状況で脚光を浴びているのが、実力でSiを大きく上回るSiC(炭化ケイ素)やGaN(窒化ガリウム)を用いたパワー半導体である。例えば、SiCをインバーターに用いたときの損失は、従来のSi素子を用いたときに比べて1/100になる可能性がある。 ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス、16nm FinFETを用いたSRAMを開発

ルネサス エレクトロニクスは2014年12月、16nmプロセス世代以降の車載情報機器用SoC(System on Chip)向け回路技術を開発したと発表した。 FinFETプロセスをめぐる技術開発は競争激化へ

FinFETプロセスをめぐる技術開発は競争激化へ

FinFETプロセスを採用したチップは、既に100種類以上がテープアウトされているという。以前は、プロセス技術ではIntelが突出していたが、現在はTSMCやSamsung ElectronicsなどのファウンドリもIntelとの差を縮めてきていて、接戦が繰り広げられている。