ナノインプリント開発の進展状況をキヤノンが講演(4)〜「パーシャルフィールド」への対処:SEMICON West 2015リポート(11)(2/2 ページ)

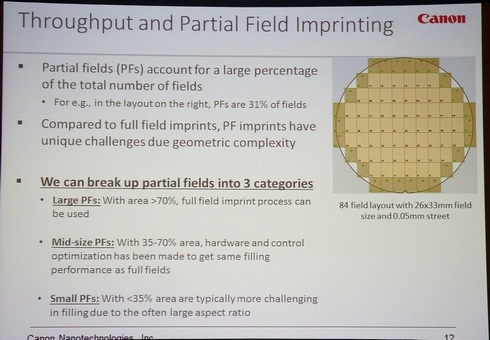

今回は、露光の際にシリコン・ウエハー周辺部で発生する現象「パーシャルフィールド」をもう少し掘り下げて解説しよう。このパーシャルフィールドについてキヤノンは、3種類に分けて対処しているという。

パーシャルフィールドが抱える課題

ただしパーシャルフィールドでは、フルフィールドと違ったプロセス・パラメータが要求される。例えばフルフィールドではレジストを露光領域全体に滴下できるが、パーシャルフィールドでは、レジストを滴下可能な領域が限定されている。そして滴下可能な部分のサイズや形状などが個々のフィールドごとに違う。つまり、滴下条件がフィールドごとに異なる。

またパーシャルフィールドでは個々に形状が違うので、レジストをフルに充てんするまでの所要時間が違う。講演者のResnick氏は触れていなかったようだが、たぶん、テンプレートの最適な加圧条件も違う。26カ所のパーシャルフィールドに対して個別に対応していたのでは、パラメータの扱いが複雑になりすぎる。

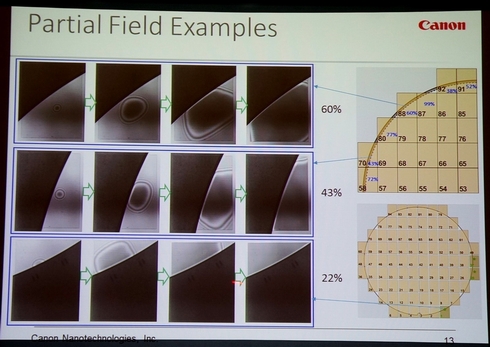

パーシャルフィールドでレジストが充てんされる様子とウエハー上の位置。左がレジストの動き。4コマの写真で示した。最も左がレジストの滴下直後で、右に向かって時間が進行する。なお数字の%は、露光領域面積の何%をウエハーが占めているかを示す。右はウエハー上におけるパーシャルフィールドの位置(クリックで拡大)

パーシャルフィールドを3種類に分けて対処

講演者のResnick氏は、パーシャルフィールドをその大きさに応じて3種類に分けて対処していると説明した。「ラージ(大)」と「ミッドサイズ(中)」、「スモール(小)」である。

「ラージ(大)」は、ウエハー部分が露光領域の70%を超えるフィールドを指す。この場合は、フルフィールドと同じ条件(パラメータ)を適用する。

「ミッドサイズ(中)」は、ウエハー部分が露光領域の35%〜70%を占めるフィールドである。この場合は、ハードウェアと制御パラメータを最適化することで、フルフィールドと同等のレジスト充てん性能を達成する。

「スモール(小)」は、ウエハー部分が露光領域の35%に満たないフィールドを指す。この部分では、フルフィールドと同じ性能を達成することはかなり難しいとする。

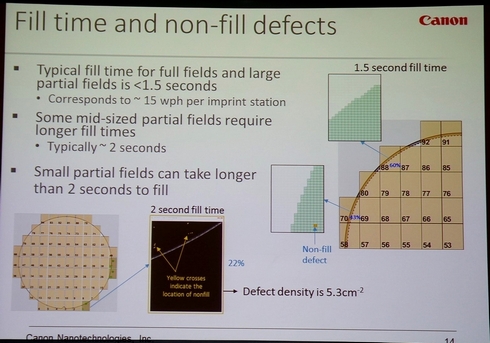

フルフィールドと「ラージ(大)」の場合、レジストの充てん時間は1.5秒未満で済む。これは、インプリント装置1台当たりで15枚/時間のウエハー処理速度に相当する。

「ミッドサイズ(中)」のパーシャルフィールドになると、必要な充てん時間が長くなることがある。その場合は、2秒くらいの時間がかかるとする。

「スモール(小)」のパーシャルフィールドでは、所要時間は「ミッドサイズ(中)」よりも長くなる。どのくらいの長さが必要かは、明示されなかった。

パーシャルフィールドにおけるレジスト充てんの実験結果。右上は「ミッドサイズ(中)」のパーシャルフィールドに対して1.5秒間の充てん時間でインプリントを実施した結果。60%のパーシャルフィールドでは欠陥が発生していないが、43%のパーシャルフィールドでは欠陥(レジストの未充てん欠陥)が発生している。左下は、「スモール(小)」のパーシャルフィールドに対して2秒間の充てん時間でインプリントを実施した結果。数多くの欠陥(レジストの未充てん欠陥)が発生している。欠陥密度は1cm2当たりで5.3個である(クリックで拡大)

(次回に続く)

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

ニコンが展望する10nm以下のリソグラフィ技術(前編)

ニコンが展望する10nm以下のリソグラフィ技術(前編)

本稿では、リソグラフィ技術の将来を14nm世代から5nm世代まで展望するシンポジウムにおける、ニコンの講演内容を紹介する。同社は、10nm世代にArF液浸露光技術を適用する場合、2つの大きな課題があると指摘した。「EPE(Edge Placement Error)」と「コストの急増」だ。 3D XPointから7nmプロセスまで――Intel CEOに聞く

3D XPointから7nmプロセスまで――Intel CEOに聞く

2015年8月18〜20日に開催された「IDF(Intel Developer Forum) 2015」において、Intel CEOのBrian Krzanich氏にインタビューする機会を得た。新メモリ技術として注目を集めた「3D XPoint」からAltera買収まで、率直に話を聞いてみた。 ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

ASMLがEUVリソグラフィ開発の最新状況を公表(1)〜ArF液浸の限界

今回は、コストとパターン形成の2点について、ArF液浸とEUV(極端紫外線)リソグラフィを比べてみよう。ArF液浸では、10nm世代になるとステップ数と重ね合わせ回数が破壊的な数値に達してしまう。これがコストの大幅な上昇を招く。さらに、ArF液浸とEUVでは、10nm世代の配線パターンにも大きな差が出てくる。 ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

ムーアの法則をできる限り進める――TSMCが7nmプロセス向けにEUV装置を発注

TSMCが、ASMLにEUV(極端紫外線)露光装置2台を発注していたことが明らかになった。TSMCは、EUVリソグラフィによって7nmプロセスの実現を目指すとみられている。2015年末には7nmプロセスを適用したチップのリスク生産が開始される可能性がある。