僩儔僀僋儔僗僞偺儌僶僀儖丒僾儘僙僢僒傗僼儖HD12Ch張棟SoC偑搊応丗暉揷徍偺僨僶僀僗捠怣 ISSCC 2016僾儗價儏乕乮2乯乮1/2 儁乕僕乯

崱夞偼丄僙僢僔儑儞4乣6偺僴僀儔僀僩傪徯夘偡傞丅僙僢僔儑儞4偱偼丄MediaTek偑丄ARMv8A傾乕僉僥僋僠儍偺CPU僐傾傪10屄撪憼偡傞儌僶僀儖丒僾儘僙僢僒傪斺業偡傞丅摦嶌廃攇悢偺堘偄偵傛偭偰CPU僐傾傪3偮偺僋儔僗僞乮僩儔僀僋儔僗僞乯偵暘偗偰偄傞傕偺偩丅儖僱僒僗 僄儗僋僩儘僯僋僗偼丄僼儖HD偺價僨僆張棟傪12僠儍儞僱儖幚峴偡傞幵嵹忣曬婡婍岦偗SoC傪敪昞偡傞丅

僇儞僼傽儗儞僗弶擔屵屻偺拲栚島墘

丂慜夞偵懕偒丄ISSCC 2016偺媄弍島墘僙僢僔儑儞偐傜丄2016擭2寧1擔乮寧乯屵屻偵敪昞梊掕偺島墘榑暥偺僴僀儔僀僩傪偍撏偗偟傛偆丅

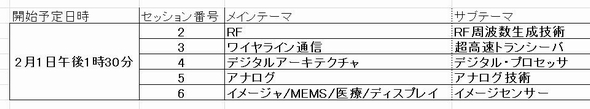

丂偙偺帪娫懷偼丄僙僢僔儑儞2偐傜僙僢僔儑儞6傑偱偺5杮偺僙僢僔儑儞偑摨帪暲峴偵恑峴偡傞丅儊僀儞僥乕儅偼僙僢僔儑儞2偑乽RF乿丄僙僢僔儑儞3偑乽儚僀儎儔僀儞捠怣乮桳慄捠怣乯乿丄僙僢僔儑儞4偑乽僨僕僞儖丒傾乕僉僥僋僠儍乿丄僙僢僔儑儞5偑乽傾僫儘僌乿丄僙僢僔儑儞6偑乽僀儊乕僕儍/MEMS/堛椕/僨傿僗僾儗僀乿偱偁傞丅偙偺拞偱慜夞偼丄僙僢僔儑儞2偲僙僢僔儑儞3偺拲栚島墘傪偛徯夘偟偨丅

丂崱夞偼丄僙僢僔儑儞4乣僙僢僔儑儞6偺拲栚島墘傪偛徯夘偟傛偆丅

14nm僾儘僙僗傪嬱巊偟偨嵟愭抂偺PC梡僾儘僙僢僒乽Skylake乿

丂僙僢僔儑儞4偺僒僽僥乕儅偼乽僨僕僞儖丒僾儘僙僢僒乿偱偁傞丅崅偄張棟惈擻傪幚尰偟偮偮丄徚旓揹椡偺憹戝傪梷偊傞僾儘僙僢僒媄弍偑懕弌偡傞丅Intel偑偼偠傔偵丄14nm僾儘僙僗偵傛傞戞6悽戙偺Core傾乕僉僥僋僠儍乮奐敪僐乕僪柤丗Skylake乯傪嵦梡偟偨SoC乮System on a Chip乯傪敪昞偡傞乮島墘斣崋4.1乯丅22nm僾儘僙僗偵傛傞戞4悽戙偺Core僾儘僙僢僒偵斾傋丄張棟惈擻摉偨傝偺徚旓揹椡傪敿暘偵尭傜偟偨偲偡傞丅

丂MediaTek偼丄ARMv8A傾乕僉僥僋僠儍偺CPU僐傾傪10屄撪憼偡傞儌僶僀儖婡婍梡傾僾儕働乕僔儑儞丒僾儘僙僢僒偺奐敪惉壥傪斺業偡傞乮島墘斣崋4.3乯丅摦嶌廃攇悢偺堘偄偵傛偭偰CPU僐傾傪3偮偺僋儔僗僞偵暘偗偰偄傞丅1.4GHz偺僋儔僗僞偲2.0GHz偺僋儔僗僞丄2.5GHz偺僋儔僗僞偱偁傞丅

丂儖僱僒僗 僄儗僋僩儘僯僋僗偐傜偼2審偺敪昞偑偁傞丅1審偼丄僼儖HD偺價僨僆張棟傪12僠儍儞僱儖幚峴偡傞幵嵹忣曬婡婍岦偗SoC偱丄儖僱僒僗僔僗僥儉僨僓僀儞偍傛傃儀僩僫儉偺Renesas Design偲嫟摨偱奐敪偟偨乮島墘斣崋4.4乯丅H.264偺僨僐乕僪張棟偲榗傒曗惓張棟偵昁梫側帪娫偼崌寁偱70儈儕昩偲抁偄丅徚旓揹椡偼197mW偱偁傞丅傕偆1審偼帺摦幵梡偺婡擻埨慡婯奿ISO26262 ASIL-B偵懳墳偟偨僿僥儘僕僯傾僗丒儅儖僠僐傾SoC偱丄儖僱僒僗僔僗僥儉僨僓僀儞偲嫟摨偱敪昞偡傞乮島墘斣崋4.5乯丅1帪娫摉偨傝偱10亅7偲掅偄丄儔儞僟儉丒僴乕僪僂僃傾屘忈棪傪払惉偟偰偄傞丅

Copyright © ITmedia, Inc. All Rights Reserved.