ルネサス「世界最速/高集積」の画像処理用SRAM:16nm世代の自動運転車向けSoCに展開へ(1/3 ページ)

ルネサス エレクトロニクスは2016年6月16日、16nm以降のFinFETプロセスを用いたSoCに内蔵するためのSRAM技術として、「世界最高の集積性と速度を実現したSRAMを開発した」と発表した。

シングルポートと同じセル構造で

ルネサス エレクトロニクス(以下、ルネサス)は2016年6月16日、16nm以降のFinFETプロセスを用いたSoC(System on Chip)内蔵用SRAMとして、0.8V動作時313ピコ秒(以下、ps)の読み出し時間と6.05Mビット/mm2の面積当たり容量を実現する技術を開発したと発表した。ルネサスでは「世界最高の集積度と高速性能を達成した」とし、16nm FinFETプロセスを用いて展開している車載情報機器用SoCの次世代品に開発した技術を適用していく方針。

画像処理用途で求められる高速性

発表したSoC内蔵用SRAM技術は、16nm以降の微細プロセスで主流となっているFinFETプロセスにおいて、集積度を高めながら、高速読み出し性能を両立するための技術として開発した。集積度を高めることでSoCのコストと消費電力を抑制し、読み出しの高速化によりリアルタイムな画像処理を必要な車載用途などの要求に応えることを狙った。

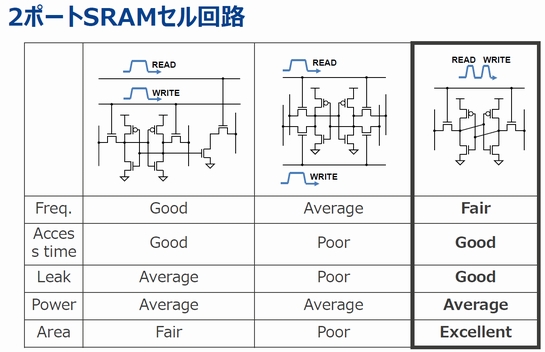

SRAMは、書き込む/読み出す仕組みにより「シングルポート」「デュアルポート」「2ポート」の3つのタイプがある。シングルポートは、1ビット当たりのトランジスタ使用数が6個(以下、6Tr構成)でワード線が1本の単純なセル構造で集積性に優れるが、読み書きポートが1つで読み出しと書き込みを同時に行えず、速度性能は劣る。

デュアルポートは、2つの読み書きポートを持ち、2つのポートが別個に読み出し/書き込み動作ができ速度面で優れるが、8Tr構成になり、面積/リーク電力が増大する課題があった。また、同時にメモリアクセスする際に、十分な動作マージンを確保するための工夫が必要となるため、速度の低下や動作下限電圧の悪化などの課題も存在する。

2ポートSRAMセルの回路図と特長(表中、右端)。左2つはともに、デュアルポートSRAMセルで、左から2番目は2015年にルネサスが開発したFinFETに最適化した左右対称型のデュアルポートSRAMセル (クリックで拡大) 出典:ルネサス エレクトロニクス

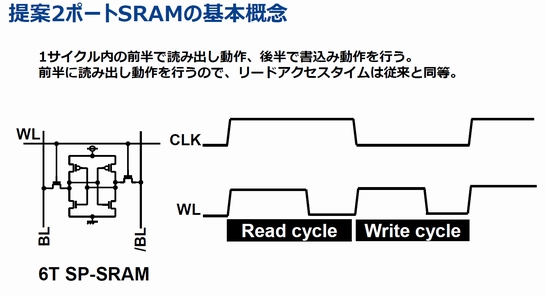

これらに対し、2ポートタイプは、シングルポート同様の6Trのセル構成ながら1クロックサイクル内に同時に読み出しと書き込み動作が独立して行えるもの。デュアルポートのように2つのポートが同時に読み出す、同時に書き込むといった動作はできないが、デュアルポートの2つのポートがそれぞれ読み出し、書き込みを行った場合と同様に1クロックサイクル内で行える高速性を持つ。加えて、2ポートタイプは、1クロックから2つのクロックを生成し、読み出し→書き込みの順に行うため、速度低下を招く同時アクセス対策が必要なく、読み出し/書き込みの同時動作であれば、結果としてデュアルポートよりも速度性能を高められる。

ただ、1ポートやデュアルポートでは、1クロックサイクルで1つのポート当たり1つの動作で済むのに対し、2ポートでは2動作する必要がある。「これまでも、2ポートSRAMの概念はあり、比較的低速な動作で済み、コスト重視の領域では採用されてきたが、高速性重視の用途では、トランジスタ性能が動作速度に追い付かず、実現できていなかった」とする。

そうした中で、「FinFET構造の登場で、トランジスタ素子の性能が大きく高まり、2ポートSRAMで十分な高速性を実現できるようになった」とし、ルネサスは高速2ポートSRAMの開発に着手し、今回、製品に搭載可能な技術として開発を完了させた。

Copyright © ITmedia, Inc. All Rights Reserved.