GFの7nm FinFETプロセス、2018年にも製造開始へ:ギガビット未満の混載MRAMもサポート(2/3 ページ)

GLOBALFOUNDRIES(GF)が、7nm FinFETプロセスの開発計画を発表した。2018年後半には同プロセスでの製造を開始する予定だという。さらに、同じく2018年には、22nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスで製造するチップにおいて、ギガビット未満の低容量の混載MRAM(磁気抵抗メモリ)をサポートする予定だ。

ファウンドリー事業は安定していないIntel

GLOBALFOUNDRIESのその他のライバル企業は、最先端技術を保有しながらも、ファウンドリー部門の規模が小さいという、Intel(インテル)だ。

アナリストたちは、「世界最大の半導体メーカーであるIntelは現在、プロセス技術を手掛けるあらゆる企業の一歩先を行く。しかし、ファウンドリー事業はまだ安定していない」という見解で一致している。Intelは現在、10nmプロセス開発を加速していて、一部の観測筋はこれについて、「GLOBALFOUNDRIESとTSMCの7nmプロセスに匹敵する技術になる」との見方を示している。Intelの10nmプロセスにおいて、EUV(極端紫外線)リソグラフィを利用できるようになれば、クアッドパターニングが不要になるとみられている。

Samsungも10nmプロセスを開発中

Samsung Electronics(サムスン電子)は、Intelに次ぐ世界第2位の半導体メーカーであるが、ファウンドリー市場では、第3位の座をめぐり競争を繰り広げているところだ。SamsungもTSMCと同様、10nmプロセス技術を開発しており、2017年以降に適用チップの生産を拡大していく予定だという。

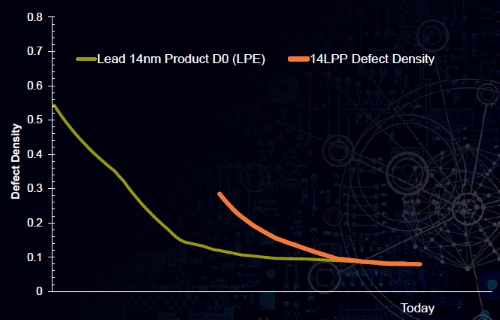

Samsungは、EUVリソグラフィを利用した最先端プロセスで製造したチップを2019年までに出荷することを目指しているともいわれる。ただしEUVリソグラフィ技術は、チップを量産できるだけのスループットや信頼性を確立しているとはとてもいえない状況だ。SamsungとGLOBALFOUNDRIESは2014年4月、14nm FinFETプロセスの提供が可能になったと発表した。

7nmプロセスで、ダイサイズは14nm比で30%低減

GLOBALFOUNDRIESのCTO(最高技術責任者)を務めるGary Patton氏は「われわれは技術をライセンス提供したいわけではない。自分たちで開発したいのだ」と述べている。同氏はIBMで45nm、32nm、22nmおよび14nmプロセスの開発に携わった人物である。

Patton氏は、GLOBALFOUNDRIESの7nmプロセスについて「ダイサイズは14nmに比べて30%縮小する。1mm2のチップに1700万ゲートを集積できる」と説明している。

7nmプロセスは、14nm/16nmプロセスと同様にプレミアムクラウドやスマートフォン向けプロセッサを対象としている。ARMの「Cortex-A72」コアは、これらのプロセスで製造した場合、3.5GHz以上の周波数で動作するという。

7nmプロセスは17層のメタルレイヤー(金属層)で構成されていて、重要なレイヤーのクアッドパターニングに対応するために80〜84枚のマスクが必要だという。現時点での同プロセス最大の課題は、トランジスタをチップに配線する中間のメタルレイヤーにおける寄生容量と歩留まりの低さである。

Jha氏は、「これらは、半導体業界の鬼門と言ってもよい問題だ」と述べている。

Patton氏は、7nmプロセスで使われるチャンネル材料については積極的にコメントしなかった。信号速度を上げるにはSiGe(シリコンゲルマニウム)のようなIII-V族化合物を使う必要があると指摘する研究者もいる。「新しい材料が必須であることは間違いない。コバルトを採用するメーカーは多いが、当社は別の材料を用いている。ただし、それについてはコメントを控えたい」(同氏)

Copyright © ITmedia, Inc. All Rights Reserved.