不揮発SRAMでプロセッサの待機時電力を大幅削減:不揮発性パワーゲーティング(1/2 ページ)

東京工業大学の菅原聡准教授らによる研究グループは、マイクロプロセッサの待機時電力を大幅に削減できる技術を開発した。低消費電力技術(パワーゲーティング)に不揮発性SRAMを用いることで実現した。

メニーコアプロセッサに極めて有効

東京工業大学科学技術創成研究院未来産業技術研究所の菅原聡准教授らによる研究グループは2016年11月、マイクロプロセッサの待機時電力を大幅に削減できる技術を開発したと発表した。低消費電力技術(パワーゲーティング)に不揮発性SRAMを用いることで実現した。

高性能なマイクロプロセッサや、モバイル機器などに搭載されるSoCなどでは、トランジスタのリーク電流による待機時の消費電力を、いかに低減するかが大きな課題となっている。この問題を解決するため、コア部の電源を遮断するコアレベルパワーゲーティング技術が注目されている。ところが、これまでは電源遮断時にレジスターやキャッシュメモリなどに保存されているデータを、いったん外部のバックアップメモリに転送/保存し、電源復帰時にコア内部に書き戻す必要があった。頻繁に電源遮断が行われると、エネルギー消費や書き戻すための時間が余分に必要になるなど、課題もあった。

研究グループは、コア内のレジスターやキャッシュなどを構成する各種CMOS双安定回路に不揮発性メモリ素子を組み込む、不揮発性パワーゲーティング(NVPG)技術を提案。これにより、電源遮断時でもデータをコア内に保持することが可能となった。不揮発性双安定回路は、電源遮断の時だけ不揮発記憶を行う。CMOSロジックが通常動作中は通常の双安定記憶回路として動作するため、通常は高速動作が可能である。

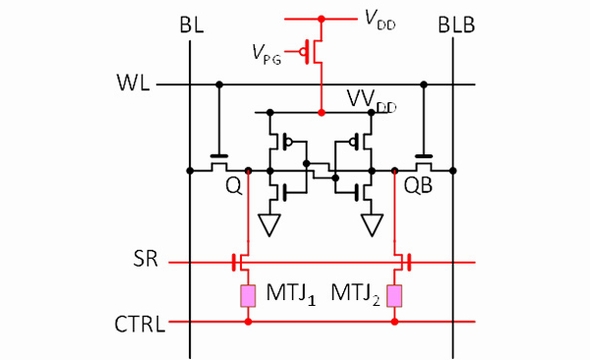

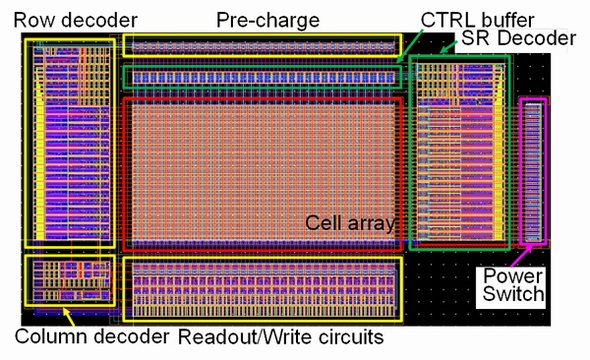

研究グループは今回、不揮発性SRAM(NV-SRAM)を試作し、NVPG実行時のエネルギー性能を解析した。NV-SRAMセルは、通常のSRAMセルに不揮発性メモリ素子である「強磁性トンネル接合(MTJ)」を接続した構造となっている。通常動作時は、トランジスタでMTJをSRAMから電気的に切り離している。また、NV-SRAMに接続されたパワースイッチで、セルへの電源を遮断する仕組みとなっている。

試作したNV-SRAMは、通常のSRAMセルよりトランジスタ数が多いものの、セルへのバイアスを工夫することで、6トランジスタSRAMセルと同等のリーク電流に抑えた。さらに、駆動方式の工夫などにより、セルアレイの各動作モードにおけるリーク電流も低減している。製造プロセスは65nmのSOTB技術を用いた。

Copyright © ITmedia, Inc. All Rights Reserved.