NANDフラッシュ、開発の視点はチップからソフトへ:Flash Memory Summit 2017(1/2 ページ)

米国シリコンバレーで開催された「Flash Memory Summit 2017」では、3D(3次元) NANDフラッシュメモリや、フラッシュストレージ向けの新しいソフトウェアなどに注目が集まった。

3D NANDフラッシュが主役

NAND型フラッシュメモリ分野では、ベンダー各社が試行錯誤しながら、新しいソフトウェアを使って新しいフォームファクタの新チップを提供している。これらの新しいNANDフラッシュは、何に利用すべきかを想定できないほど動作速度が向上している。

これは、2017年8月7〜9日に米国カリフォルニア州サンタクララで開催された「Flash Memory Summit」の感想だ。同イベントの展示会場では、初日早朝に小規模な火災が発生。スプリンクラーが作動して展示フロアが水浸しになったため、展示会の開催は中止された。あるレポーターは、台湾のInnodiskのブースで延長コードの欠陥が原因となってコンピュータラックが溶けた写真を公開したが、けが人はなかった模様だ。

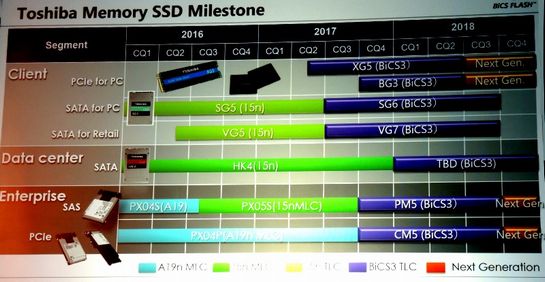

だが、このイベントの注目株が3D(3次元) NANDフラッシュであることは、デモを見るまでもなく明らかだった。Samsung Electronicsは、テラビットクラスの3D NANDフラッシュを2018年に発売すると発表している。東芝も2018年に、96層積層プロセスを適用した768Gビットのチップを出荷する。Micron Technologyは、同社の512Gビットのチップについて説明した。これら3社は、4ビット/セル(QLC)チップも提供するとしている。

3社とも、NANDフラッシュのメモリセルのスタックを形成する技術について詳細は明らかにしていない。フラッシュメモリのベテラン技術者である東芝のJeff Oshima氏は、同イベントのバックステージでEE Timesが行った短いインタビューの中で、「多くの層に均一な貫通孔を形成し、上から下の層まで同一の性能を発揮するセル構造を構築することが最大の課題だ」と語った。

Oshima氏は、「東芝はスタックのさまざまなセグメントで異なるセル設計を採用している」と説明した。ただし、同氏は、東芝がどのくらいの種類のセル設計やスタックを使用しているかについては言及しなかった。

QLCチップへの移行は、チップの書き込みサイクルに影響を及ぼすと考えられる。Oshima氏によると、「大容量を実現するために、耐久要件を緩和しても構わないとするユーザーもいる」という。

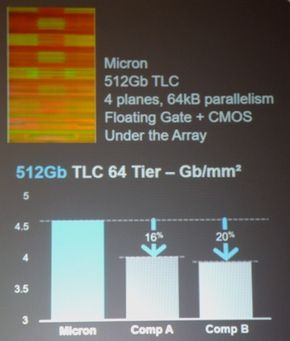

Micron Technologyは、同社の512Gビットチップは、1mm2当たりの容量で、Samsungや東芝よりも16〜20%記憶密度が高いと主張している。ただし、チップサイズや、QLCを採用する時期について詳細は明らかにしていない。

米国の半導体装置メーカーであるLam Researchは、こうした動向を受けて、今後5年間のNANDフラッシュ向け設備の投資予想額を500億米ドルから700億米ドルに引き上げた。この額は、同期間中にNANDフラッシュが40%のビット成長率を遂げるという予想に基づいて算出されている。

Lam ResearchのCTO(最高技術責任者)で3D NANDフラッシュの蒸着およびエッチングシステムを開発するRick Gottscho氏は、「3D NANDフラッシュはさらなる可能性を秘めている。100層以上が積層されたNANDフラッシュも実現できると考えている」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.