ArmのAI戦略、見え始めたシナリオ:IPベンダーならではの出方(1/4 ページ)

機械学習についてなかなか動きを見せなかったArmだが、モバイルやエッジデバイスで機械学習を利用する機運が高まっているという背景を受け、少しずつ戦略のシナリオを見せ始めている。

なかなか動きを見せなかったArm

AIというかML(Machine Learning)に関してなかなか動きを見せなかったArmだが、2018年に入ってやっとその一端を開示し始めた。

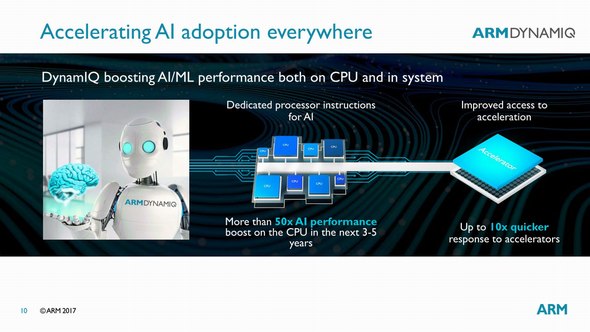

ArmがAI(人工知能)について明確に言及をし始めたのは、2017年3月の「DynamIQ」の発表時である(図1)。もっともこの時は、今後ML向けのプロセッサあるいはアクセラレータをシステムに統合する際に必要になるインフラとしてDynamIQを用意しました、という以上の話ではない。アクセラレータよりも先にインフラというかインターコネクトを用意する、というあたりが実にArmらしいという気がする。

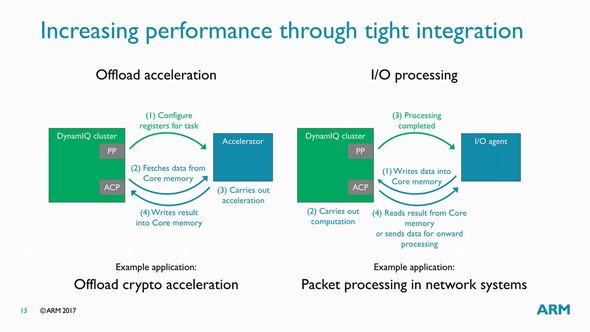

図1:当時のプレゼン資料より。これも今見直してみると、「Performanceが必要な用途はCPUで、Responseが必要な用途はAcceleratorで」と読めるあたりがいろいろ趣深い 出典:Arm(クリックで拡大)

余談であるが、なぜDynamIQがMLの対応に必要かというと、特にアクセラレータで重要だからだ。1つのプロセッサに1つのアクセラレータを直結するという構成は、特にエッジ向けのソリューションとしてVideantisやCEVAが提供するアクセラレータで想定されており、これはこれであまり考える必要はない。

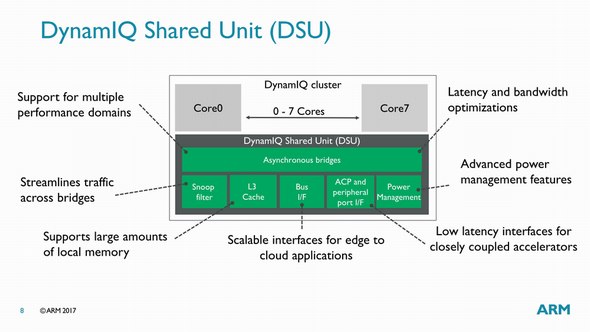

ところが「Cortex-A」ではマルチプロセッサ構成に外付けでアクセラレータを取り付けることになるから、通常のAXI4経由とかだとレイテンシが極端に大きいし、キャッシュコヒーレンシもない。これに対するArmの回答が、DynamicにACPと呼ばれる専用ポートを設けることだった(図2)。このACPに繋がれたアクセラレータは、Core 0〜Core 7の任意のCPUコアから、非常に少ないレイテンシでアクセスすることができる(図3)。感覚的には大昔の386/486の時代にWeitekのFPUを利用した時にかなり近いが、I/Oバスの先についているアクセラレータを駆動するよりもずっと高速に処理ができることになる。

図2:これは2017年8月の「HotChips 29」における資料より。ちなみに当時の質疑では、ACPはLatencyは低いが大量のデータを送るには向いてない、と説明された覚えがある 出典:Arm(クリックで拡大)

Copyright © ITmedia, Inc. All Rights Reserved.