2D NANDフラッシュと3D NANDフラッシュのセルアレイ構造:福田昭のストレージ通信(115) 3D NANDのスケーリング(3)(1/2 ページ)

今回は2D NANDフラッシュ技術と3D NANDフラッシュ技術におけるメモリセルアレイ構造の違いを、より具体的に説明する。

浮遊ゲート構造のメモリセルを使う2D NAND

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、既存技術である2D NANDフラッシュメモリの記憶容量が拡大していった様相を振り返るとともに、2D NANDフラッシュ技術から3D NANDフラッシュ技術への転換を図解した。今回は2D NANDフラッシュ技術と3D NANDフラッシュ技術におけるメモリセルアレイ構造の違いを、より具体的に説明しよう。

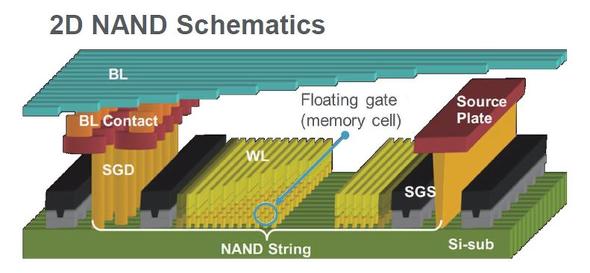

既存技術である2D NANDフラッシュを始めに説明する。メモリセルは1個のMOSトランジスタ(セルトランジスタ)で形成されている。ゲート電極は絶縁膜を挟んで2層になっており、上層のゲート電極を「制御ゲート(コントロールゲート)」、下の層ゲート電極を「浮遊ゲート(フローティングゲート)」と呼ぶ。制御ゲートはメモリセルのワード線を兼ねる。浮遊ゲートはまわりがすべて絶縁膜で囲われており、その名称の通り、電気的に浮遊(絶縁)された状態にある。

このようなセル構造を「浮遊ゲート(フローティング)」構造と呼んでいる。浮遊ゲート構造では、制御ゲートとソース、ドレイン、チャンネル(基板)に適切な電圧を与えることによって、浮遊ゲートに電子を注入したり、浮遊ゲートから電子を引き抜いたりする。浮遊ゲートに注入された電子は、電圧が加わらないときはそのまま、蓄積される。この蓄積された電子によってMOSトランジスタ(セルトランジスタ)のしきい電圧が上昇する。このしきい電圧の変化が、記憶するデータの値に対応する。

2D NANDフラッシュのメモリセルアレイでは、隣接するセルトランジスタ(ワード線が隣接するMOSトランジスタ)がソースとドレインを共有することで、水平方向にひも(ストリング)のように連なっている。これを「セルストリング」あるいは「NANDストリング」と呼ぶ。例えば16個、あるいは32個のセルトランジスタが、1本のセルストリングを構成する。セルストリングの両端は、ビット線あるいはソース線(ソースプレート)となる。

そして数多くのセルストリングを平行にレイアウトすることで、メモリセルアレイを構成する。ワード線すなわち制御ゲートは、平行にならんだセルストリングと直交するようにレイアウトされる。

Copyright © ITmedia, Inc. All Rights Reserved.