NVIDIA、Turing世代の「Tesla T4」を発表【内容追加】:Pascal世代から12倍の性能向上

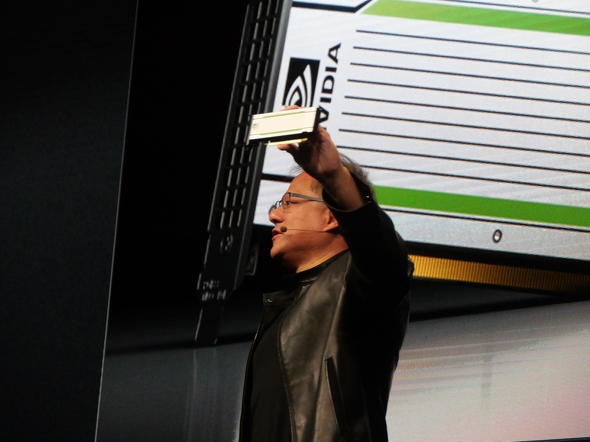

NVIDIAは2018年9月13日、同社プライベートカンファレンス「GTC Japan 2018」(2018年9月13〜14日、グランドプリンスホテル新高輪 国際館パミール)で、HPC(High Performance Computing)向けGPUボードの新製品となる「Tesla T4」を発表した。

「Turing」世代のTesla、Pascal世代から12倍の性能向上

NVIDIAは2018年9月13日、同社プライベートカンファレンス「GTC Japan 2018」(2018年9月13〜14日、グランドプリンスホテル新高輪 国際館パミール)で、HPC(High Performance Computing)向けGPUボードの新製品となる「Tesla T4」を発表した。

同チップは、先日発表された「Turing」コアを採用。Pascal世代のTesla P4と比較して、FP16(16ビット浮動小数点)を用いたディープラーニング学習モデルの推論性能で12倍の改善を果たした。消費電力は75W。既に量産体制に入っている。

320個のTensorコアと2560個のCUDAコアを実装

Tesla T4は、4×4行列の積和演算を行うTensorコアを320個、CUDAコアを2560個搭載し、演算性能はFP16を用いた場合で最高65TFLOPS、INT8(8ビット整数)で130TOPS、INT4で260TOPSと、量子化されたモデルに対してリニアな性能向上を実現した。パッケージはPCI Express(PCIe)で提供される。

また、4Uサイズのラックマウントサーバに16基のTesla T4を搭載した場合、推論性能で1PFLOPSに達するとする。

その他、推論アプリケーションに関するサービスとして「TensorRT 5」と「TensorRT inference server」も同時に発表された。Tesla T4と上記サービスを含めて、データセンター向け推論プラットフォーム「NVIDIA TensorRT Hyperscale Platform」を構成する。

各種ニューラルネットワークの最適化を行うランタイムエンジンであるTensorRT 5は、新機能としてTuringアーキテクチャのTensorコアへの対応と、ニューラルネットワークの最適化機能を強化した。TensorRT inference serverは、NVIDIAのクラウドプラットフォーム「NVIDIA GPU Cloud」より無償で入手できるコンテナ化されたマイクロサービス。このサービスにより、データセンター上で動作するアプリケーションは、GPUで動作するAI(人工知能)モデルをシームレスに統合させることができるとする。

同社では、AIを活用した推論により創出される市場が今後5年間で200億米ドル規模になると予測している。

Copyright © ITmedia, Inc. All Rights Reserved.