連載

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか:湯之上隆のナノフォーカス(9)(2/5 ページ)

Intelは2016年以降、今日に至るまで、10nmプロセスを立ち上げることができていない。一方で、配線ピッチは同等であるはずの、TSMCとSamsung Electronicsの7nmプロセスは計画通りに進んでいる。ではなぜ、Intelは10nmプロセスの立ち上げに苦戦しているのだろうか。

Intelの10nmプロセスとは

Intelは2017年12月、サンフランシスコで開催された半導体の国際学会「IEDM」で、“A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects”のタイトルで発表し、世界で初めてコバルト(Co)配線を使ったことを明らかにした。

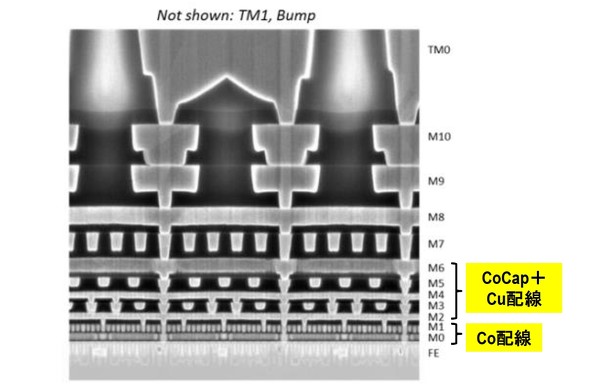

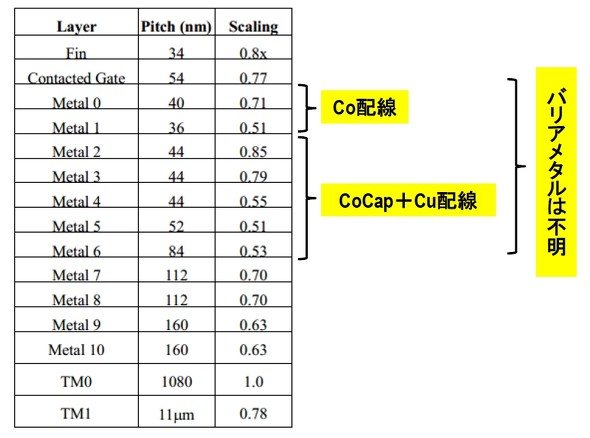

筆者は、2016年頃から、微細配線の材料がCuからCo、Ru(ルテニウム)、Mn(マンガン)などに変わるかもしれない兆候をつかんでいた。従って、この論文でIntelがCo配線を使ったことに注目した。Intelの上記論文によれば、M0とM1にCo配線を使用し、M2〜M6の配線にはCu配線とCoキャップを使ったと書かれている(図1、図2)。しかし、バリアメタル材料についての記載はない。

ここで、多層配線の構造が、バルク配線材料、バリアメタル、キャップから構成されていることを説明した上で、なぜ、CuからCoなどに配線材料が変更されなくてはならないのかを詳述する。

Copyright © ITmedia, Inc. All Rights Reserved.