光トランシーバーForm Factorの新動向(1) 〜“Beyond 400G”の議論が活発に:光伝送技術を知る(12) 光トランシーバー徹底解説(6)(3/4 ページ)

今回は、“Beyond 400G”に向けた議論とともに、Pluggableにおける3つの問題点を紹介する。

(2)トランシーバーを搭載できる数と高速配線の数

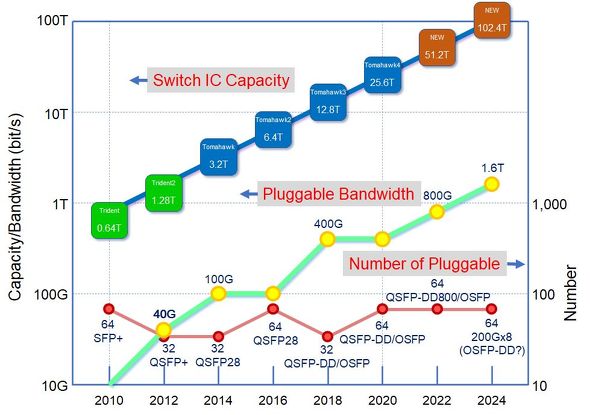

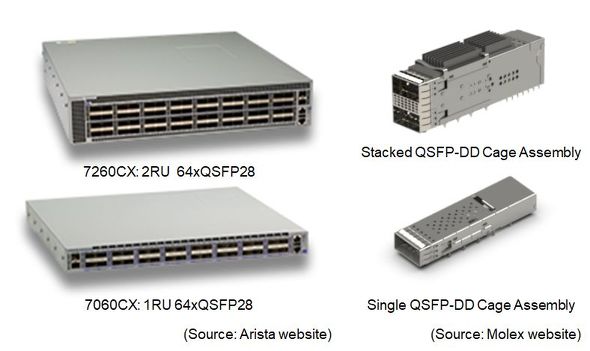

図3は、スイッチICの交換容量と、それに使用されるPluggableの伝送速度および、その数量を示したものである。先に述べたように19インチラックのシャシには、1RUで32個(最大36個)のPluggableが装着できる。64個というのは2RUの高さのシャシということだ(図4)。

32個の場合はPCBの裏表に16個ずつ搭載する(1RUフロントパネルから見ると2段x16)。64個の場合は、裏表に2階建てのケージを16個ずつ搭載する(2RUフロントパネルから見ると4段x16)。だが、図3に示すように、25.6T以降は64個=2RUで高止まりしている。光トランシーバー以外は2RUという高さを必要としていないので大きな問題である。

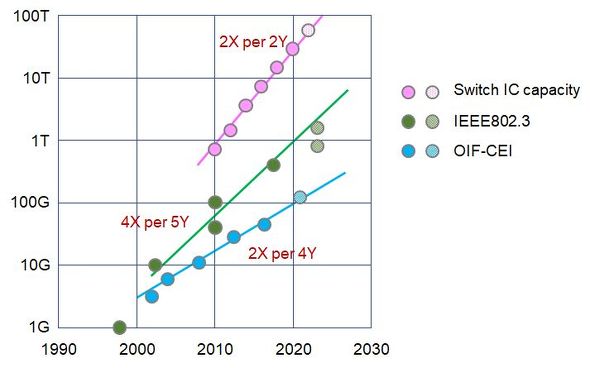

図5は、BroadcomスイッチIC交換容量(製品発表とその後の推測)、光インタフェース速度(Ethernet Allianceロードマップによる)、電気配線速度(OIFロードマップによる)をプロットしたものである。

スイッチIC交換容量が2年で2倍となっているのに対し、光インタフェース速度は5年で4倍(2.5年で2倍相当)と、辛うじて追いかけている。光インタフェースは光トランシーバーごとに装備されるため、光トランシーバーの伝送容量はスイッチICの容量増加とほぼ同期している。そのため個数は32個と64個とほぼ固定化されているのである。

光インタフェースの標準化は、ITU-TでもIEEE802.3でも3年程度の期間が必要だったため、2倍化ではなく4倍化が1990年以来の動向となっていた(ただし、40Gから100Gへは歩みを緩めた)。最近は、IEEEにおいて100Gから400Gへの4倍化の標準化をやり直したため、800Gという2倍の光インタフェースが必要になっているのが現状である。

一方の電気インタフェースは、ほぼ4年に2倍と、光インタフェースに比べて半分のスピードで増加している。この速度向上の差を埋めるために、SFPからQSFP、QSFP-DD・OSFPへと電気信号チャネル数を4x、8xと増やしてシステム要求に応えてきたのである。

今後については、先に述べた通り800Gは既にMSAが動いている。1.6Tでは、光インタフェースがPluggableのサイズで実現できたとして、電気インタフェースがどうなるかによってForm Factorが決まる。

一つは、200Gx8というQSFP-DDと、OSFPの8xで実現することである。しかしながらこれには先述した配線距離の問題が生じる。特に、QSFP-DDではカードエッジを含めたコネクター接続に課題があると思われる。また、200Gの電気インタフェース標準は2025年頃が見込まれている。従来の流れで行けば16xを検討すべきである。

もう一つは、100Gx16の電気インタフェースを有する16xの新しいForm Factorを作ることである。容易に思い付くのはOSFPのDouble Density、OSFP-DDだ。しかし、64個搭載を実現する2階建てケージでは高周波特性劣化が見込まれる。

ところで、本命と思われるOSFPの次世代、16x一列(「一列」は明確な場合省略する)のトランシーバーをSSFP(sedecim:16 SFP)と名付けるとして、そのカードエッジのパタンピッチはどうなるだろうか(先に述べたたように4xのQSFP(-DD)は0.8mm、8xのOSFPは0.6mmである)。

OSFPはカードエッジのパタン数が最小に近い。GSSGの高速信号以外は、電源Vccが4本、シリアル信号用2本、割込み・リセットピンと制御ピンそれぞれ1ピンで計8ピンとなり、それぞれ4パタンを表裏に配置している。この延長で16信号とすると、図6のようなパタン配置となる。パタン数は54である。

現在のトランシーバーのケージを搭載したボードでは、QSFPでは5.5mm、OSFPでは4.8mm程度の隙間を開けてカードエッジが並んでいる。ここでは4.8mmで計算する。425.4mm幅のボードに16個実装すると考えると、カードエッジに与えられる最大幅は(425.4mm-5mmx15)/16=21.9mmであり、パタンピッチは21.9/54=0.4mmとなる。

16xを実現するSSFPでは0.4mmピッチの高速コネクターの開発が課題となりそうだ。また同ピッチの細線ペア同軸ケーブルアレイの細線化も課題である。

Copyright © ITmedia, Inc. All Rights Reserved.