プロセスの最適化を加速する仮想製作プラットフォーム:コストと時間の削減に向けて(2/3 ページ)

高度なCMOSプロセスの微細化やメモリ技術の進化に伴い、デバイス製造における構造がますます複雑化しています。そうした中で、デバイス製造を支援する仮想製作モデリングプラットフォームを紹介します。

関心のある指標の追加

各プロセスステップに必要なのは、理解しやすく測定が容易ないくつかの幾何学的および物理的な入力パラメーターのみです。作業フローにおける次のステップは、そうした関心のある指標を特定することです。実際の工程と同じように、成膜の適合性、エッチングの異方性、選択比などのユニットプロセスパラメーターは相互に作用し、複雑な方法でデータを設計して最終的なデバイス構造に影響を及ぼします。

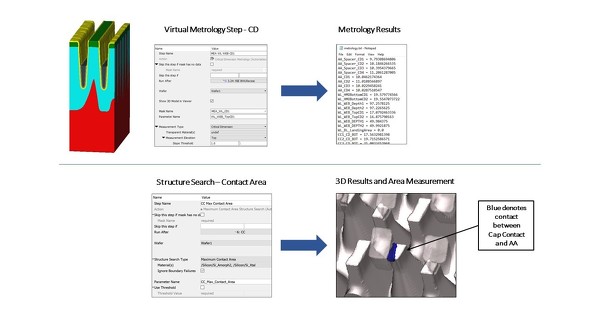

SEMulator3Dには、2種類の幾何学的計測を提供します。1つ目は仮想計測で、モデル構造を計測し、期待される寸法であることを検証することができます。2つ目は構造探索で、3Dモデル全体またはその一部を調べて、計測最大値とその位置、フィルム厚さの値と位置、線幅、コンタクト領域を特定するステップを提供します。また、材料の構成要素数もカウントするため、電気回路の短絡または断線を特定するのにも役立ちます(図2)。

構造探索は特に、工程のばらつきによって幾何学的偏位の位置が変わる場合に有効です。例えば、図2はCCとAAが接触する領域を示しています。このソフトウェアは、デバイスの故障点ともなるその位置を強調しています。

電気デバイスのシミュレーション

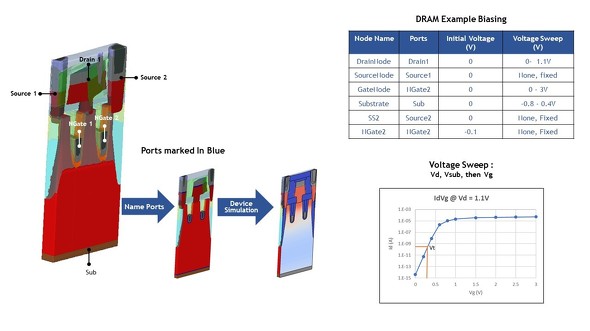

電気デバイスのシミュレーションを用いて、別の種類の特性も抽出できます。図2と同じモデルを使用したデモンストレーションでは、SEMulator3Dにおける電気的シミュレーションを行うことができます。

このソフトウェアは、3D構造でデバイスのポートと電極を特定し、温度、バンドギャップ、電子/正孔移動度といったデバイス特性をシミュレーションするのに役立ちます。手動および自動によるノード(1つのピンまたは複数が結合したピン)の特定が可能で、選択ノードに対して掃引電圧と併せて初期電圧や電流を設定できます。

図3の電気的シミュレーションの例では、2つのゲート、2つの電源、1つのドレイン、1枚の基板が示されています。エンジニアは、「DRAM Example Biasing(DRAMバイアス例)」の表に示すとおり、バイアスや初期電圧のほか、掃引電圧を自由に決定できます。

次に、ソフトウェアを使用して、閾(しきい)値電圧(Vth)、閾値下の勾配、ドレイン誘起障壁低下(DIBL)、電圧ポイントのオン電流(ION)といった関心のある指標を自動的に抽出できます。電気的性能に対する3Dプロセスの影響を考慮しながら、時間がかかる厳密なTCADモデリングを実行することなく、それらのすべてが得られます。

形状変化の影響

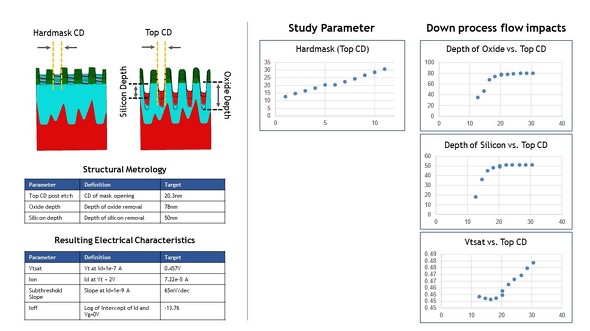

形状変化の影響に関する設計調査は、ハードマスクの限界寸法(CD)/上部のCDや、シリコン膜厚、酸化膜厚といった目標が設定された名目上のモデルの調査から始まります。SEMulator3Dは、それらの値(Vt、ION、IOFF、閾値下の勾配など)を用いて結果として生じる電気的特性を抽出します(図4(左))。

図4:【左】形状変化の影響について、名目上のモデルが調査される/【右】SEMulator3Dを使用した実験は、酸化膜厚、シリコン膜厚の感度を示し、Vtsat感度は同じ範囲内で増加する一方で20nmを超えたCDは減少変化する

この調査の目的は、図4のハードマスクのCDを12nmから30nmへと2nmずつ増やして変化させながら、シリコン膜厚や酸化膜エッチングなどの残りの構造パラメーターをモニタリングすることです。この変化は、フロー初期のプロセスステップを変動させることによって行い、下流のプロセスステップはモデルにおける変化に予測的に対応します。

図4(右)は、ゲートエッチ後に非直線的に反応しているハードマスクCDの変化を示しています。酸化膜厚と上部シリコン膜厚は、CDが小さいほど上部のCDの影響を受けやすくなりますが、CDが大きくなると飽和します。その一方で、20nmの公称値を超えてCDが変化するとVtsatが大幅に増加します。このように、SEMulator3Dの指標は、形状がたった一度変化するだけでさまざまな反応を示しており、エンジニアは自らが選択したパラメーターで形状変化の影響を調べることができます。

Copyright © ITmedia, Inc. All Rights Reserved.