ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術:湯之上隆のナノフォーカス(35)(1/6 ページ)

今回は、「IEDM2020」から先端パッケージの講演をいくつか紹介する。そこで見えてきたのは、今後「ムーアの法則」のけん引役となるかもしれない「チップレット」技術と、その開発競争が進んでいるということだった。

「IEDM2020」で先端パッケージ技術に注目した

2020年12月、半導体デバイスの国際学会「IEDM」がオンデマンドとライブを併用したバーチャル方式で行われた。12月5日から視聴可能になった発表時間約80分のチュートリアルが6件、翌12月6日から視聴できるようになった発表時間40〜60分のショートコースが14件、12月14日から開始された本会議には41のテクニカルセッションがあり、1件約20分の発表が232件あった。

これら全てを合計すると約5960分=約99時間となり、1日8時間ずつ視聴しても12〜13日かかる計算になる。当初は、2020年6月にやはりオンライン形式で開催されたVLSIシンポジウムのように、総括記事を書きたいと思っていた(関連記事:「1nmが見えてきたスケーリング 「VLSI 2020」リポート」)。しかし、年末年始の繁忙期と重なったこと、そして、この発表件数と視聴時間に恐怖感を覚えたため、それは断念した(なお、この原稿を書いている現在もオンデマンドによる視聴が可能な状態となっている)。

そこで、今回のIEDMの報告に際しては、ポイントを「先端パッケージ技術」の一点に絞ることにした。その理由を以下に述べる。

現在、最先端の微細化を突き進んでいるTSMCが、10年ほど前からInFO(Integrated Fan-Out)やCoWoS(Chip-on-Wafer-on-Substrate)と呼ぶパッケージ技術を開発していることは知っていた。ところが、TSMCだけでなく、10nmの微細化でつまずいてしまったIntelも、ファウンドリービジネスでTSMCをキャッチアップしたいSamsung Electronics(以下、Samsung)も、こぞって先端パッケージ技術を開発しつつある。今回のIEDMでも、これら3社の先端パッケージ技術の発表があった。

これはなぜなのかと思っていたところ、IEDMとほぼ同じ時期にオンライン方式で開催されたSemicon Japan主催の「Semi Technology Symposium」で、SBR Technologyの西尾俊夫氏の講演“Challenge of Chiplets Package to Improve AI Chip Performance”を視聴して、「チップレット」という概念が理解できたことにより、その疑問が氷解したのである。

その「チップレット」という視点でIEDMの発表を眺めてみると、半導体産業の景色が変わってしまった。それどころか、今後、ムーアの法則は、スローダウンし始めた微細化ではなく、チップレットを取り入れた先端パッケージ技術がけん引するとすら思うようになったほどだ(我ながら随分な宗旨替えである)。

そして、2021年2月9日付の日経新聞が、TSMCが茨城県つくば市に約200億円を投資して後工程の材料開発の拠点を設けることを報じたが、これが事実なら、日本の後工程の材料メーカーにとって大きなチャンスになるかもしれないとも考えた。

本稿では、まず、チップレットとは何か、なぜチップレットが必要なのかを論じる。その際、前述した西尾氏の講演内容を参考にさせて頂く(西尾氏にはその旨を連絡し快諾して頂いた)。その上で、今回のIEDMで、TSMC、Samsung、Intelが、どのような先端パッケージ技術の発表を行ったかを紹介する。最後に、今後、チップレットを取り入れた先端パッケージ技術がムーアの法則をけん引するであろう将来展望を述べたい。

チップレットとは何か?

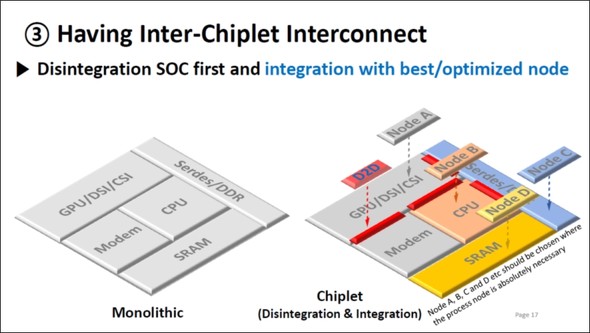

今回のIEDMのショートコースで、SamsungのSE-Ho You氏が“From Package-Level to Wafer-Level Integration”で発表したスライドが、チップレットの将来像の一つを示している(図1)。

図1:チップレットとは何か? 出典:SE-Ho You (Samsung), “From Package-Level to Wafer-Level Integration”, IEDM2020, SC1(クリックで拡大)

従来は、一つのテクノロジーノードで、CPU、GPU、モデム、SRAM、Serdes/DDRなどの機能を詰め込んだSoC(System on Chip)を一度に製造していた。

これを、機能別に、それぞれ最適なテクノロジーノードで製造する。図1の右側では、ノードAでGPUを、ノードBでCPUを、ノードCでSerdes/DDRを、ノードDでSRAMを、それぞれ別のウエハーで製造し、これらをインテグレーションすることによって1チップ化していることが分かる。

このように、別々のウエハーで製造したチップをつなぐことにより、ある一つの機能を持つSoCを形成する技術がチップレットの概念である。

では、なぜ、チップレットが必要不可欠になってきたのだろうか? その背景には、先端半導体が処理しなければならないデジタルデータ量が指数関数的に増大しているという事情がある。

Copyright © ITmedia, Inc. All Rights Reserved.