ムーアの法則 次なるけん引役は「チップレット」 〜IEDM2020に見る先端パッケージ技術:湯之上隆のナノフォーカス(35)(3/6 ページ)

今回は、「IEDM2020」から先端パッケージの講演をいくつか紹介する。そこで見えてきたのは、今後「ムーアの法則」のけん引役となるかもしれない「チップレット」技術と、その開発競争が進んでいるということだった。

ビッグデータとAI半導体の処理能力

2020年9月17〜18日に開催されたThe Second AI HW SummitでIntelは、AI半導体が処理するデータ量が3.5カ月で2倍、1年で約10倍、2年で64〜100倍になることを指摘した(図6)。

図6:AIが処理するデータは3.5ヶ月で2倍、2年で64〜100倍に増大 出典:MOOR Insights and Strategy, AI Hardware: Harder Than It Looks(クリックで拡大)

このように指数関数的に増大するデータ量を、ASIC(つまりSoC)のAI半導体が対処できるだろうか? 図7は、半導体のロードマップITRS(International Technology Roadmap for Semiconductors)に替わって登場したIRDS(International Roadmap for Devices and systems)の2018年度版に掲載されているSoCにおけるCPUとGPUのコア数および、CPUのスループット(処理能力)を示している。

2020年にCPU13個、GPU27個だったSoCのコア数は、2031年にそれぞれCPUが95個(7.3倍)、GPUが97個(3.6倍)になると予測されている。その中のCPUのスループットは、2020年の0.32 TFLOPS/sec、から、2031年に8.25倍の2.64 TFLOPS/secになると予測されている。ただし、これは発熱による速度低下を考慮しない場合であり、熱による速度遅延が起きれば2031年に約3倍の0.95 TFLOPS/secにしかならない。

なお、TFLOPS/secとは、tera floating-point operations per secondの略で、コンピュータの処理能力を表す単位であり、tera(テラ)は1兆、FLOPS(フロップス)は1秒間に行える浮動小数点演算の回数を表す。従って、1 TFLOPSは毎秒1兆回の浮動小数点演算を行えることを意味する。

さて、2020年から2031年にかけては、SoCのCPUのコア数は7.3倍の95個になり、発熱による速度低下を考えなければCPUの処理速度は8.25倍の2.64 TFLOPS/secになるとの予測である。従って、2031年に登場すると想定されるSoCのAI半導体は、2020年に対して、7.3×8.25=約60倍の処理能力を持つと計算できる。

しかし、AI半導体が処理する必要なデータ量は、図6でIntelが示した通り、2年で64〜100倍になるため、最小値の64倍としても2031年には2020年の64の5乗以上=10億倍必要になり、コア数を増やし、各コアのスループットを向上させるだけでは全く処理能力が足りないことになる。

コア数に伴うSoCのコストの増大

増え続けるデータ量に対して、SoCのAI半導体の処理能力は全く足りない。しかし、少しでも処理能力を向上させるためには、SoCのコア数を増大させ、各コアのスループットを増大させ続けるしかない。そのためには、スケーリングを続けることが必須となる。しかし、それに伴ってウエハーコストが高騰することが大問題となる。

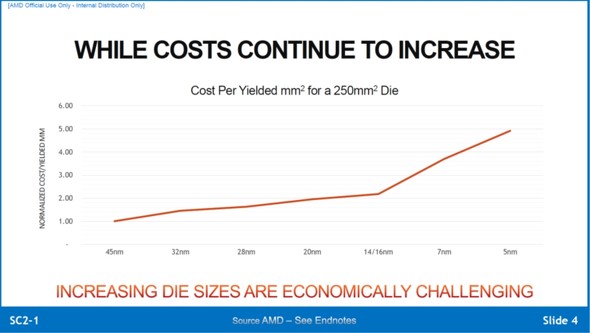

図8は、2020年のVLSIシンポジウムのショートコースで、AMDのSamuel Naffziger氏が“Chiplet Meets The Real World -- Benefits and Limits of Chiplet Designs”において発表した、スケーリングとチップコストの関係を示したものである。

図8:スケーリングとチップコストの増大 出典:Samuel Naffziger (AMD), “Chiplet Meets The Real World -- Benefits and Limits of Chiplet Designs ”, VLSI2020, Short Course 2-1.(クリックで拡大)

45nmノードで製造したチップコストを「1」と規格化した場合、微細化が進むにつれてチップコストは増大し、5nmでは5倍になると計算されている。このグラフでは、14/16nm以降のグラフの傾きが急峻になっているが、恐らくEUV(極端紫外線)リソグラフィ技術を使うことを想定しているからだと思われる。

このようにスケーリングを続けると、チップコストが増大するのは間違いないが、それでもAI半導体の処理能力の向上のために、TSMCもSamsungも微細化を続けている。これに加えて、コア数の増大も必須となるが、それはスケーリングの推進以上にコスト高騰を招く。そして、これらを解決する手段として登場したのが、チップレットである。

Copyright © ITmedia, Inc. All Rights Reserved.