TSMCの微細化は2nmまで? 以降はパッケージングが肝に:2021 Technology Symposium(1/3 ページ)

ムーアの法則はこれまで長年にわたり、「半導体チップのトランジスタ密度は、2年ごとに2倍になる」との見解を維持してきたが、3nmプロセスにおいて数々の問題が提示されるようになった。それでもTSMCは、引き続き楽観的な見方をしているようだ。

ムーアの法則はこれまで長年にわたり、「半導体チップのトランジスタ密度は、2年ごとに2倍になる」との見解を維持してきたが、3nmプロセスにおいて数々の問題が提示されるようになった。それでもTSMCは、引き続き楽観的な見方をしているようだ。

ムーアの法則については、間もなく行き詰まりを見せるのではないかと何年も前からいわれてきたが、それがあとどれくらいなのかという点については議論の余地が残っている。また新しい技術の中には、”トランジスタ密度の倍増”に依存することなく、持続的な性能向上を実現できるというものもある。今後、技術が登場するタイミングによって、広範にわたる影響が及ぶことになるだろう。TSMCのCEOであるC. C. Wei氏は、2021年6月1〜2日に開催された「TSMC 2021 Technology Symposium」において、世界の発電量全体の1%を超える電力を消費するデータセンターを一例として取り上げている。

同氏は、「世界全体のデータセンターの電力使用量は、2010〜2030年の間で5〜40倍に増加すると予測されている。なぜこんなにも予測幅が大きいのだろうか。その1つの理由として挙げられるのが、設置面積を正確に予測することが難しいという点だ。また、検討すべき可変的な要素が多過ぎるということもある。その中には、『ムーアの法則は存続することが可能なのか』ということも含まれる」と述べる。

Wei氏は「悲観的な予測の場合は、その背景に、『ムーアの法則が間もなく終わりを迎えるため、半導体プロセス技術によって実現する効率向上では、もはやデータ/計算性能の需要に対応することができない』という考え方がある」と指摘する。

TSMCの半導体微細化ロードマップは、2nmプロセスで終了するとみられる。このため同社は、今後も引き続き、電力需要を低下させながらトランジスタ密度と処理能力の向を実現すべく、パッケージングと新しい材料の技術を組み合わせる方向へと進んでいる。

Wei氏は、「われわれは、ムーアの法則と”Beyond Moore”の実現を目指し、2D(2次元)での微細化と3D IC(3次元積層IC)の両方に関して、信頼性のある予測可能なロードマップを策定した。今後も引き続き、最先端のロジック技術を提供することにより、2D微細化が今もまだ健在であるということを実証していきたい」と述べる。

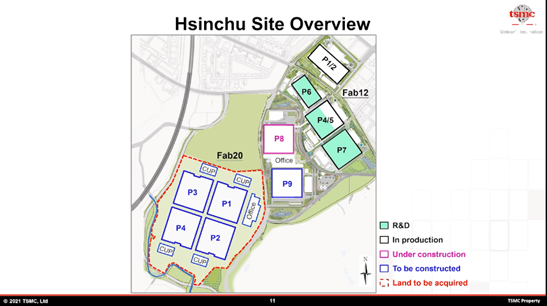

TSMCによると、現在のところ、まだ2nmプロセス以降の微細化の予定はないという。同社はTSMC 2021 Technology Symposiumの中で、台湾の新竹(Hsinchu)に建設予定の、同社初となる2nmプロセス工場の詳細を一部明らかにした。ただし、工場の場所についてはいくつか詳細を提示したものの、それ以外の生産時期や能力などについては明かそうとしなかった。

Copyright © ITmedia, Inc. All Rights Reserved.