Rain NeuromorphicsがアナログAIのデモチップをテープアウト:ReRAM利用で高性能を実現(1/2 ページ)

Rain Neuromorphicsが、脳型アナログアーキテクチャのデモチップをテープアウトした。ランダムに接続されたメモリスタの3Dアレイを用い、ニューラルネットワークトレーニング/推論などを超低消費電力で計算することが可能だという。

Rain Neuromorphicsが、脳型アナログアーキテクチャのデモチップをテープアウトした。ランダムに接続されたメモリスタの3Dアレイを用い、ニューラルネットワークトレーニング/推論などを超低消費電力で計算することが可能だという。

AI(人工知能)計算向けとして完全なアナログハードウェアに切り替えることにより、AIワークロードによって消費される電力量を大幅に低減することができる。一部の商用チップは現在、アナログPIM(Processor in Memory)技術を適用しているが、ネットワークレイヤー間のデジタル変換が必要なため、消費電力量がかなり大きい。既存のアナログデバイスに何らかの制限があるということは、AIモデルのトレーニング向けとしては利用できないということを意味する。それは、現在AIトレーニング向けとして広く採用されているアルゴリズム「バックプロパゲーション(誤差逆伝搬法)」との互換性がないからだ。Rain Neuromorphicsの狙いは、完全なアナログチップを実現することにより、新しいハードウェアとトレーニングアルゴリズムとを組み合わせながら、こうした問題を解決することにある。

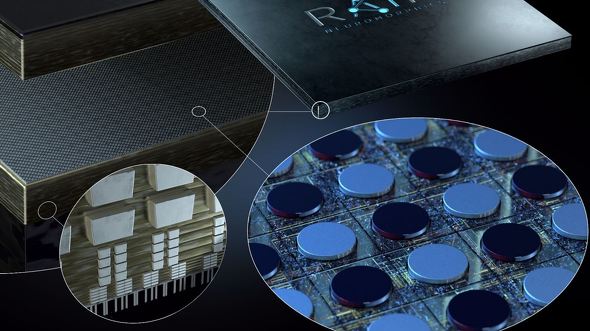

Rain Neuromorphicsは過去1年間にわたり、ハードウェアの方向性を変化させてきた。アナログコンピューティングチップは、メモリスタ素子を並べたアレイと、フラッシュなどのメモリセルを使用した商用チップとを組み合わせて使う。同社はかつて、ランダムに蒸着された抵抗ナノワイヤを使用していたが、NAND型フラッシュメモリのプロセスを活用した3D製造技術と組み合わせたメモリスタ素子として、抵抗変化メモリ(ReRAM)を選択した。その結果、完全にリソグラフィーをベースとしたコンフィギュレーションが生み出されたのだ。

またこのチップは、フラッシュアレイのVBL(Vertical Bit Line)向けに開発された技術を採用しているため、ReRAMを多層構造メモリにスケーリングすることもできる(現在のフラッシュアレイは、100層以上を備えることが可能)

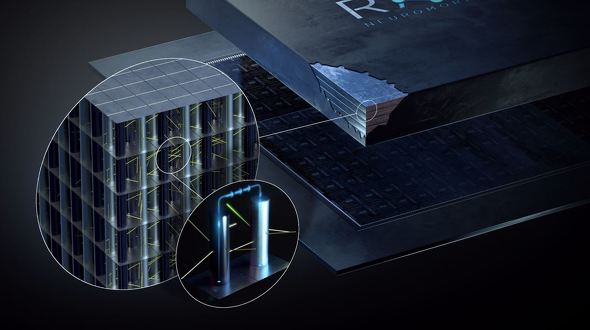

チップ底部のCMOS層は、ニューロンを表している。VBLを使用して構築されたカラムは、軸索を表す。このカラムは、メモリスタ材料で被覆されている。ランダムに構成されたデンドライトが軸索とリンクし、ニューロンを相互に接続する(全ての層のデンドライトがカラムに接触している点を、シナプスと見なすことができる)

Rain Neuromorphics社チップ底部。ニューロンを表すCMOS層の上には、軸索に相当する列が垂直ビットライン技術を用いて作られている。カラムは、入力と出力を表すために2つの異なる色で表示されている[クリックで拡大] 出所:Rain Neuromorphics

Rain NeuromorphicsのCTO(最高技術責任者)を務めるJack Kendall氏は、米国EE Timesのインタビューに応じ、「われわれとしては、実際に非常に脳に近い構造を実現することができ、とても誇らしく思っている。脳の軸索や樹状突起と同じ構造であるため、これ以上の優れた方法はないといえるだろう」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.