HARエッチングとナノスケールパターニングで実現するメモリロードマップ:ラムリサーチ(1/3 ページ)

メモリ技術は市場の要求に応じて、より高密度かつ高性能、そして新素材や3D構造、高アスペクト比(HAR)エッチング、EUV(極端紫外線)リソグラフィへと向かっている。本稿では、これらの方向性を見据えた、Lam Researchの開発内容を紹介する。

メモリ技術は市場の要求に応じて、より高密度かつ高性能、そして新素材や3D構造、高アスペクト比(HAR)エッチング、EUV(極端紫外線)リソグラフィへと向かっています。半導体製造工場がコスト効率のよいソリューションを得られるよう、Lam Research(ラムリサーチ)は製造技術の3年から5年先を見据えた課題の検討を行っています。

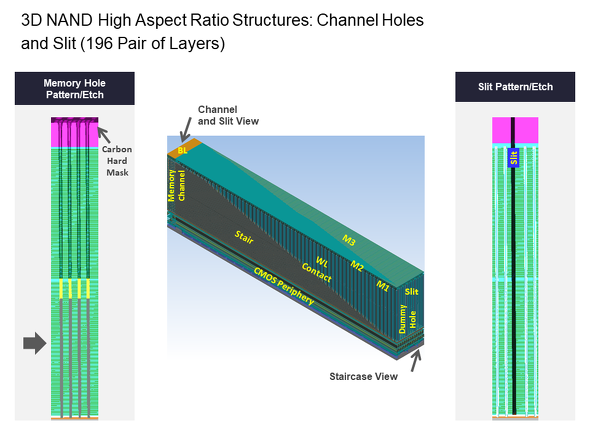

3D NAND型フラッシュメモリ(以下、単に3D NAND)の記憶容量を増やす方法の一つは、その三次元積層構造(スタック)の積層数を増やすことです。ただし、スタックの高さが増すにつれ深刻な技術的困難に直面します。構造の安定性を保つことはもちろん、積層数が増えるということは、各ワード線にアクセスするチャネルが深くなり、ビット線に接続されたチャネルを分離する、スリットの幅が狭くなるということを意味します(図1)。

図1:増大するエッチングの課題。3D NANDスタックが128層をこえると、その高さは7μmに近づき、必要なチャネルホールやスリットは高アスペクト比(HAR)形状に変わる[クリックで拡大] 出所:ラムリサーチ

HARエッチングの課題

3D NANDの製造工程は、酸化膜と窒化膜の各層を交互に成膜するところから始まります。続いてハードマスクを成膜し、チャネルを垂直にエッチングするための開口部を形成します。ここがHARエッチングの最初の課題になります。

最先端のフラッシュメモリは128層を超える構造へ移行しつつあり、スタックの深さは7μm近く、ハードマスクの厚みは2〜3μm程度、チャネルホールのアスペクト比は90〜100に達しつつあります。

図1に示す「ステアケース」構造を作った後には、多層膜にスリットを形成する難しい工程へと続きます。ハードマスク層を成膜し、開口部をパターニングして、これら全ての層を分離するスリットをシングルステップのエッチングで形成します。最後に窒化膜層を取り除き、タングステンのワード線を形成します。

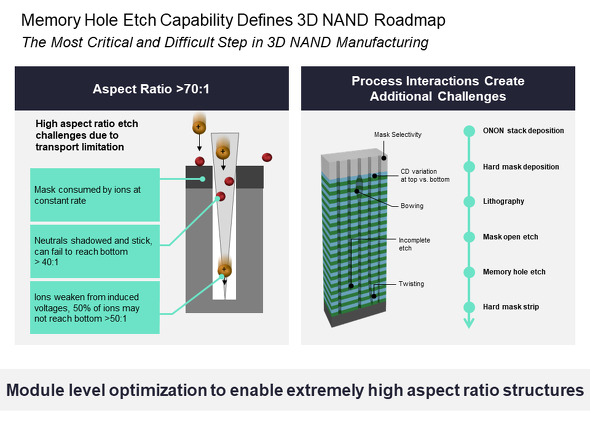

反応性イオンエッチング(RIE)を成り立たせるためには、イオンと中性粒子の間に生じる相乗効果(シナジー)が欠かせません。しかしながらHAR構造に対しては、このシナジーは複数の機序によってさまたげられ、簡単に失われてしまいます。

まず、圧力が高いと、イオンはプラズマシース内で散乱し、通常、異方的なイオンのエネルギーや角度の分布が拡がります。そのためイオンはパターン内への入射をさまたげられたり、あるいは大きな角度を持って入射し、構造の上部や側壁に衝突したりしてしまいます。このようなイオンの「シャドーイング」によりイオンと中性粒子のフラックス比はシナジーから遠ざかります(図2)。

図2:イオンと中性粒子のシャドーイング、粒子輸送のアスペクト比依存性は、イオンの角度分布同様、CD(パターン寸法)のばらつき、エッチストップ、ボーイング(Bowing:湾曲)、ツイスティングなどの形状異常を引き起こす大きな要因となる[クリックで拡大] 出所:ラムリサーチ

HAR構造の底部までイオンを到達させるには、イオンのエネルギーを大きくする必要がありますが、同時にマスクの削れ量も増加するため、マスクを厚くする、あるいはマスク材料の革新が必要になります。

さらに、パターン側壁へ衝突するイオンが、チャネルのパターン寸法(CD)を必要以上に拡げてしまう問題があります。この「ボーイング(Bowing:湾曲)」(図2)が大きくなりすぎると、2つのホールがつながってしまうこともあります。

もう一つの重大な問題は、パターンに沿って形状が湾曲するツイスティングで、(プラズマに印加される)RF系の高次高調波歪によるチャージの影響でイオンの角度分布が、わずかに変化することにより引き起こされます。

Copyright © ITmedia, Inc. All Rights Reserved.