開発担当が語る、ソニーの2層トランジスタ画素積層型CIS:車載イメージセンサー事業の歴史も(1/2 ページ)

ソニーセミコンダクタソリューションズ(以下、SSS)は2022年1月25日、グループ理念や事業活動について紹介するイベント「Sense the Wonder Day」をオンラインで開催した。イベントでは、同社が前年12月に発表した「2層トランジスタ画素積層型CMOSイメージセンサー技術」について開発担当者が説明したほか、車載事業の創業メンバーが車載事業の歴史を語るなどした。

ソニーセミコンダクタソリューションズ(以下、SSS)は2022年1月25日、グループ理念や事業活動について紹介するイベント「Sense the Wonder Day」をオンラインで開催した。イベントでは、同社が前年12月に発表した「2層トランジスタ画素積層型CMOSイメージセンサー(CIS)技術」について開発担当者が説明したほか、車載事業の創業メンバーが車載事業の歴史を語るなどした。

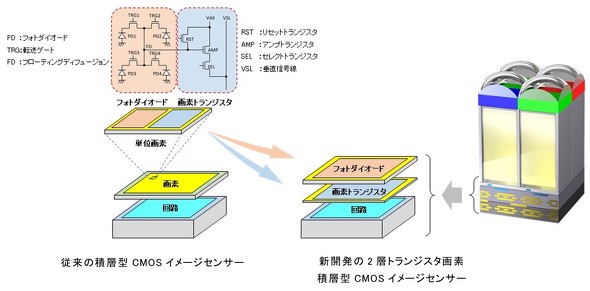

フォトダイオードと画素トランジスタを別基板で積層

2層トランジスタ画素積層型CMOSイメージセンサー技術について説明したのは、このデバイス構造設計と3Dインテグレーション開発を担当したSSS第2研究部門の中澤圭一氏だ。

同氏はプロセスインテグレーション開発を専門領域とし、デバイス構造の設計から新規プロセス技術の導入といった業務を主に担当。これまでロジック、CCD、CMOSイメージセンサーおよび次世代メモリ開発に携わり、現在はモバイル向けの新規イメージセンサーの研究開発を行っている。

SSSは2021年12月、「世界で初めて」(同社)2層トランジスタ画素積層型CMOSイメージセンサー技術を開発したと発表した。この技術は、従来の裏面照射型CMOSイメージセンサーでは同一基板上で形成していたフォトダイオードと画素トランジスタの層を、別々の基板に形成し上下に積層。これによって従来比約2倍の飽和信号量を確保し、ダイナミックレンジ拡大とノイズ低減といったイメージセンサーの高画質化を実現するというものだ。また、転送ゲート(TRG)以外のリセットトランジスタ(RST)、セレクトトランジスタ(SEL)、アンプトランジスタ(AMP)などの画素トランジスタをフォトダイオードのない別の層に形成したことでアンプトランジスタのサイズの拡大が可能となり、夜景などの暗所撮影時に発生しやすいノイズも大幅に低減するという。

製造フロー途中でウエハーを貼り合わせる新プロセス技術で実現

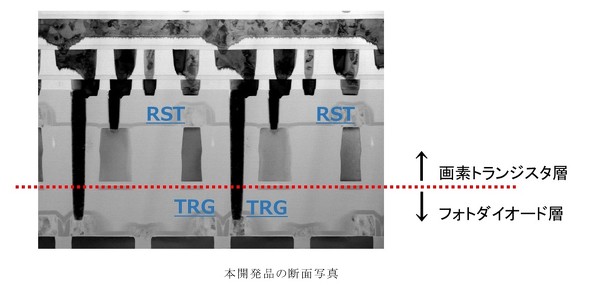

中澤氏は、「今回の技術では、1画素単位で異なる基板同士を接続させる積層デバイスを実現したが、それにはフォトダイオードと画素トランジスタをナノメートルの精度でアライメントする技術が必要になる。その実現のために、『3Dシーケンシャルインテグレーション』という新たなプロセス技術を導入した」と説明した。

これは、従来技術のように完成したウエハー同士を貼り合わせるのではなく、製造フローの途中で新しいウエハーを張り合わせ、その後も製造フローを継続する技術で、「具体的には、フォトダイオードを形成後にシリコンウエハーを張り合わせ、その上に画素トランジスタを形成するプロセス技術だ。これによりアライメント精度は張り合わせではなくリソグラフィーで決定され、高精度なアライメントが実現可能となる」(同氏)

中澤氏は、同技術実現に向け「大きな課題」だった点として、ウエハー積層後の製造工程における「熱」を挙げた。同氏によると、従来構造では接合技術に要求される耐熱性は400℃だったのに対し、今回の構造を実現させるためには1000℃以上の耐熱性が必要だといい、「この課題に対し、ソニーの持つウエハー接合技術を進化させ、また、本構造に合わせたトランジスタを構築することで、今回のデバイス開発に成功した」と語った。

また、今回実現した構造では、フォトダイオードと画素トランジスタが物理的に分離されることから、構造的な制約を受けることなくそれぞれを最適化することが可能になるという。中澤氏は、「発表では主にダイナミックレンジ拡大やノイズ改善といった画素性能向上が期待できることに触れたが、実際には特性改善だけではなく新たな機能の追加など多くの可能性を持ったデバイスだ。現在、研究開発部門では、まさにここに関してさまざまな検討が行われている」と説明していた。

本技術は半導体や電子デバイスの国際会議「IEDM(International Electron Devices Meeting) 2021」(2021年12月11〜15日)で発表されたが、中澤氏は、「発表後、非常に大きな反響があり、市場からも高い期待が寄せられていることを実感している」と語っていた。

Copyright © ITmedia, Inc. All Rights Reserved.